DFI3.1协议的4.8, 这段章节内容涉及DFI协议中的频率比率(Frequency Ratios),尤其是当MC(内存控制器)和PHY(物理层)使用不同频率时,DFI协议如何进行协调。DFI协议支持在不同频率下的信号传输,并且涉及多个方面的时序调整和信号同步。

4.8 Frequency Ratios Across the DFI

在DDR内存子系统中,通常会将PHY的时钟频率设置得高于MC的时钟频率。这样做的目的是提高数据传输的速率,即PHY以比MC更高的频率进行数据传输。DFI协议规定了在MC和PHY之间如何协调不同的频率,这也涉及到多个时序和数据传输层面的调整。

主要概念

- MC和PHY的时钟频率比(Frequency Ratio):

- 在DFI协议中,MC和PHY之间的时钟频率比通常是1:2或1:4。这意味着PHY的时钟频率是MC时钟频率的2倍或4倍。例如,如果MC的频率为1GHz,则PHY的频率可以是2GHz(1:2比率)或4GHz(1:4比率)。

- DFI时钟:

- DFI时钟是MC时钟的频率,所有的DFI信号都以MC时钟为参考。

- PHY时钟和DRAM时钟同步:

- DFI中的PHY时钟与DRAM时钟始终是同步的,且PHY时钟的频率是内存数据速率的一半。例如,DDR4的PHY时钟可能为1.6GHz,而内存的数据速率为3.2Gbps。

- 数据传输速率:

- 由于PHY的频率更高,PHY可以在每个DFI时钟周期内执行多个命令,从而提高数据传输的速率。例如,在1:2的频率比率下,PHY可以在每个MC时钟周期内进行2次数据传输。

- 频率比率的影响:

- 频率比率影响读取数据和写入数据的接口。它可能导致读数据旋转(read data rotation)和数据重同步(resynchronization)。

- DFI时钟和PHY时钟之间的频率比也影响了CA(地址)和CRC(循环冗余校验)校验错误的检测和处理。

dfi_freq_ratio 信号

dfi_freq_ratio信号:MC使用该信号向PHY传递频率比设置。这个信号仅在使用频率比协议的设备中需要。通过dfi_freq_ratio信号,MC告知PHY它的频率相对于PHY的频率比是多少(例如1:2或1:4)。

相关章节

如果你需要进一步了解频率比协议对读写数据接口的影响,DFI协议的文档中提供了几个相关章节:

- 4.8.2 Interface Signals with Frequency Ratio Systems:介绍频率比系统中的接口信号。

- 4.8.3 Write Data Interface in Frequency Ratio Systems:详细说明频率比系统中写数据接口的行为。

- 4.8.4 Read Data Interface in Frequency Ratio Systems:说明频率比系统中读数据接口的行为。

- 4.8.4.1 DFI Read Data Rotation:介绍在频率比系统中,读数据的旋转机制。

- 4.8.4.1.1 Read Data Resynchronization:介绍读数据的重同步机制。

- 4.10.2.1 CA and CRC Parity Errors in Frequency Ratio Systems:解释频率比系统中如何处理CA和CRC校验错误。

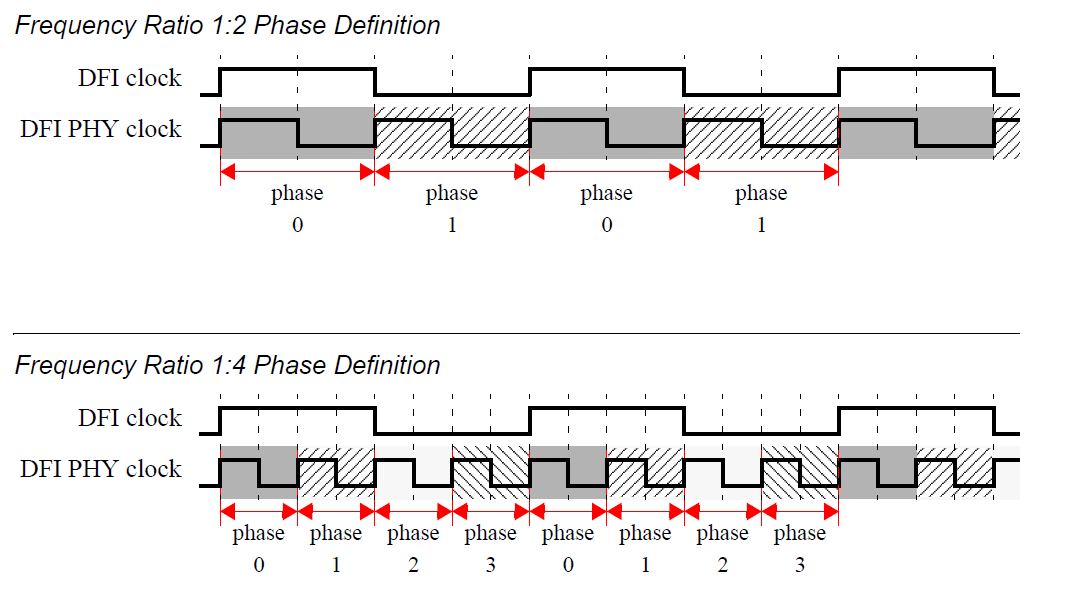

4.8.1 Frequency Ratio Clock Definition

在频率比系统中,DFI时钟和DFI PHY时钟之间的相位对齐非常重要。为了保证时序的准确性,DFI协议要求两者的时钟相位对齐,并且支持1:2或1:4的频率比。

- 时钟相位对齐:DFI时钟和PHY时钟必须在相位上对齐。这是指它们的上升沿(rising edge)需要同步。

- 时钟相位定义:在1:2或1:4频率比下,DFI PHY时钟的相位数量与DFI时钟的相位数量的比率一致。例如,在1:2的频率比下,DFI PHY时钟的相位数量是DFI时钟的两倍,DFI信号需要相应调整以保持同步。

- 时钟相位的图示:章节提到,Figure 35 和 Figure 36 显示了1:2和1:4频率比系统的时钟相位定义。这些图帮助理解如何根据频率比调整相位,从而确保正确的时序。

4.8.2 Interface Signals with Frequency Ratio Systems

这一章节讨论了在不同频率比系统中,DFI协议如何定义和使用接口信号,尤其是在MC(内存控制器)和PHY(物理层)之间传递命令和数据时的信号安排和时序。频率比系统(比如1:2、1:4等)需要在多个时钟相位上协调信号的传输,DFI协议通过增加“_pN”或“_wN”的后缀来管理这些相位。下面是对这一部分内容的详细解释:

1. 信号按相位定义

- 按相位定义的信号:在频率比系统中,所有的写数据和读数据信号都基于DFI时钟的每个相位进行定义。DFI时钟是MC与PHY之间传输信号的基准时钟,所有信号的时序都必须以DFI时钟为参考。

- 时序约束:PHY在驱动信号时,必须确保信号的变化仅发生在DFI PHY时钟的第0相位(phase 0)。这样做的目的是允许MC在完整的DFI时钟周期内捕获信号的变化。

2. 频率比系统中的命令传输

DFI协议支持在每个相位上传输一个独立的命令,这就意味着MC可以在一个DFI时钟周期内向PHY发送多个命令。为了实现这一点,DFI定义了向量化命令格式,使得在频率比系统中能够传递关于命令的额外信息。

命令信号的后缀形式

命令信号的命名规则:在频率比系统中,控制信号、写数据接口以及读数据使能信号都会带有一个后缀“_pN”,其中N表示相位编号。

例如,在一个1:2频率比系统中,dfi_address信号会被分成两个信号:dfi_address_p0:表示相位0上的地址信号dfi_address_p1:表示相位1上的地址信号

对于读数据接口,dfi_rddata、dfi_rddata_valid 和 dfi_rddata_not_valid 信号会带有后缀“_wN”,其中N表示数据字的编号。具体到数据字,通常相位0的后缀(如

dfi_rddata_w0)是不必要的。举例:对于一个1:2频率比系统,MC可能在第0相位上发送一个命令,而在第1相位上发送另一个命令。命令和数据的时序在相位之间可能有所不同,因此需要通过这种方式来管理相位间的命令和数据流。

3. 灵活的系统设置

DFI协议在频率比系统中提供了一定的灵活性,特别是在MC如何输出命令的方式上:

- MC的灵活性:MC可以选择在一个或多个相位上发送命令。如果MC选择在多个相位上发送命令,它并不要求在所有相位上都必须驱动每个信号,只有在命令发送的相位上,MC才需要驱动信号。

- 例外情况:有两个信号—

dfi_cke_pN和dfi_odt_pN,这两个信号不能总是在与其他命令相同的相位上驱动。为了提供时序上的灵活性,这两个信号必须在所有相位上都被实现,以确保系统能够正确处理命令。 - PHY的要求:PHY必须能够接受在所有相位上发送的命令。即使MC只使用某些特定的相位来发送命令,PHY也需要能够正确地解析这些命令并处理信号。

4. 不同信号的实现方式

不同信号可以在相位间有不同的实现方式,具体的实现可以依赖于系统设计。例如:

- 在一个2T(双相)实现中,

dfi_ras_n_pN、dfi_cas_n_pN和dfi_we_n_pN等信号可以由MC在所有时钟相位上驱动。 - 然而,

dfi_cs_n_pN(芯片选择信号)可能只在一部分相位上由MC驱动。

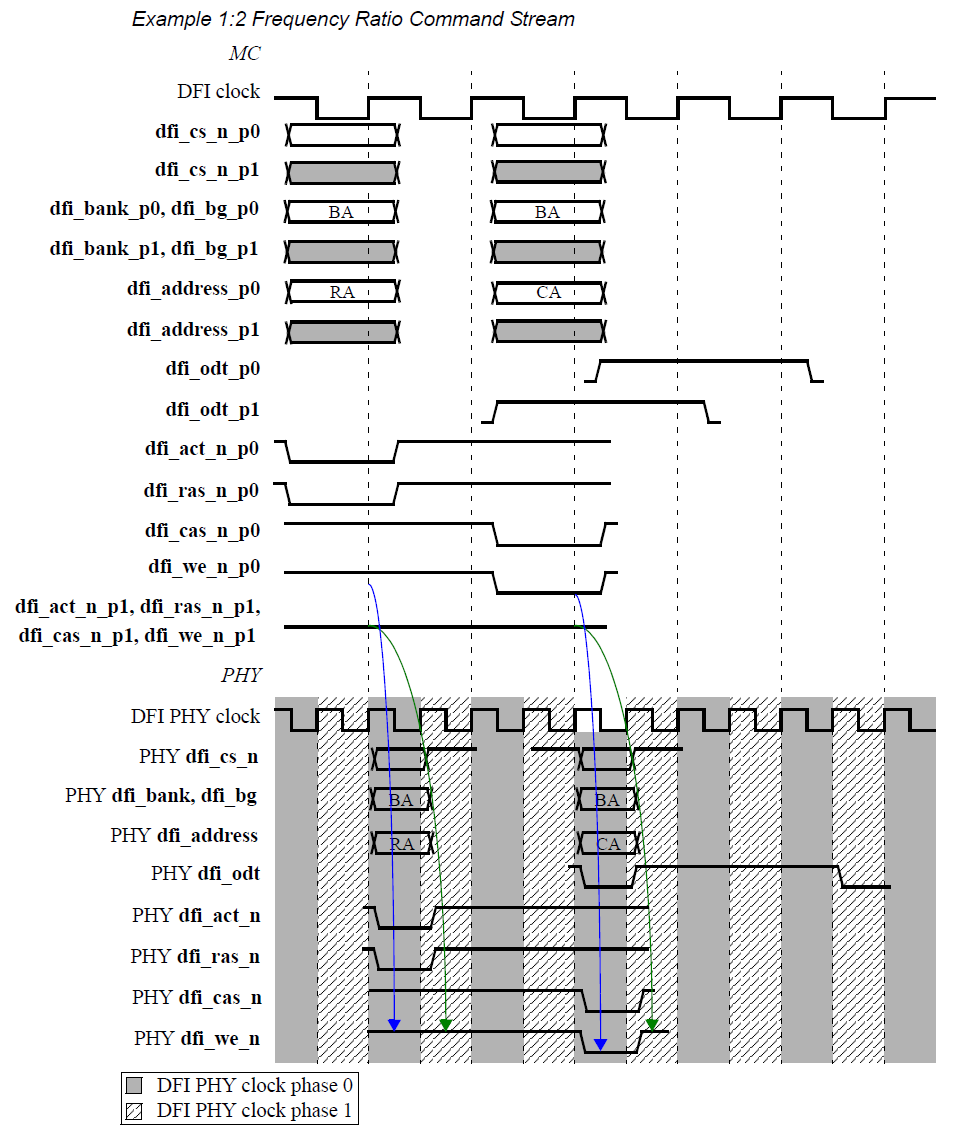

5. 命令流的示例

- Figure 37: Example 1:2 Frequency Ratio Command Stream图,这个图展示了在一个1:2频率比系统中的命令流示例。图中表示,命令仅在第0相位发送,而第0和第1相位的命令值会不同。尽管如此,ODT(On Die Termination)信息却同时出现在两个相位上。图示的PHY时序仅供说明,命令总线的信号值并不总是相同的,也并非总是等于1。

- 图38,“1:4频率比命令流示例”表示相同的示例,但采用的是1:4频率比系统。命令仅在相位0上发送,ODT信息则在所有相位上提供。PHY时序仅用于说明。

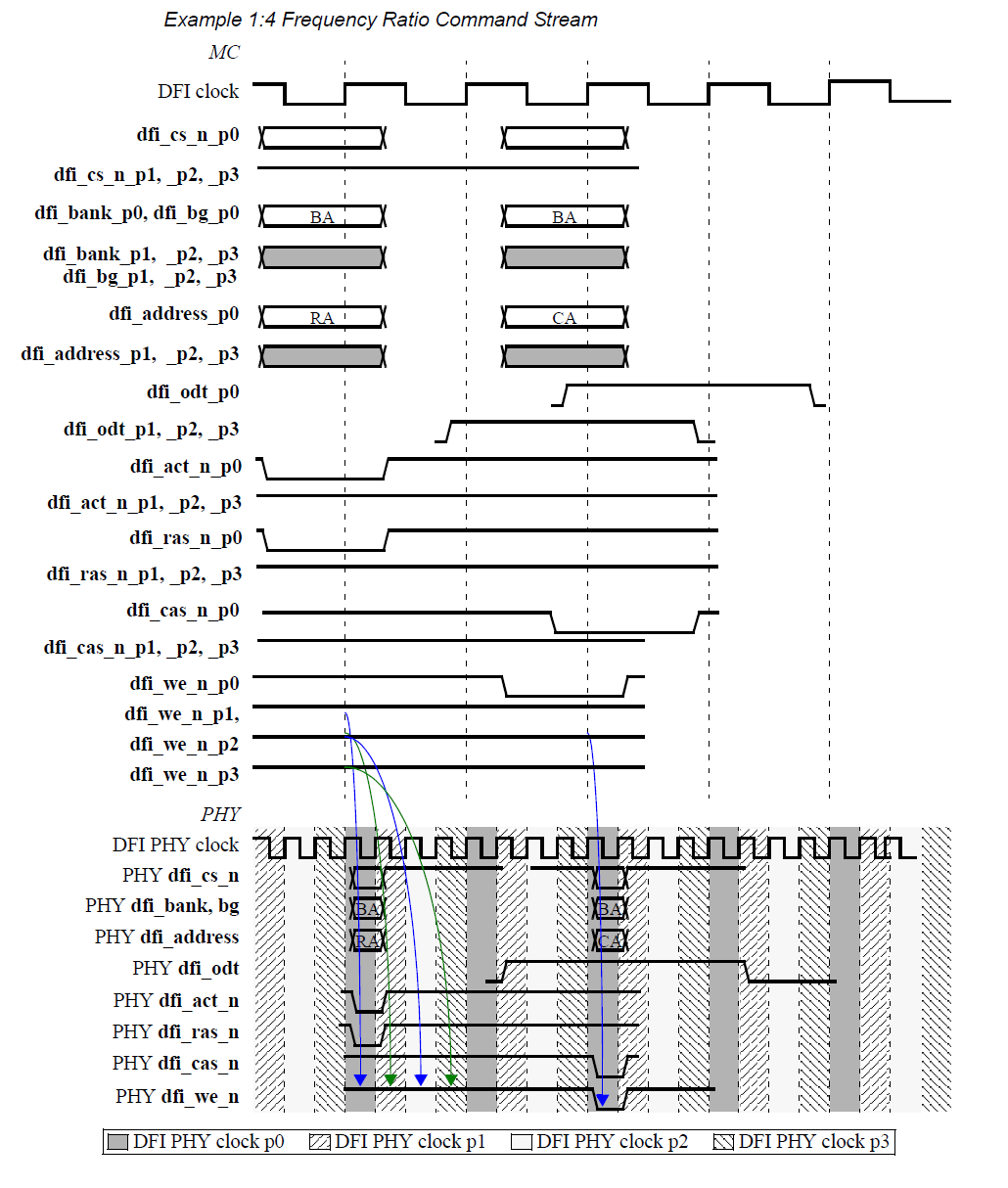

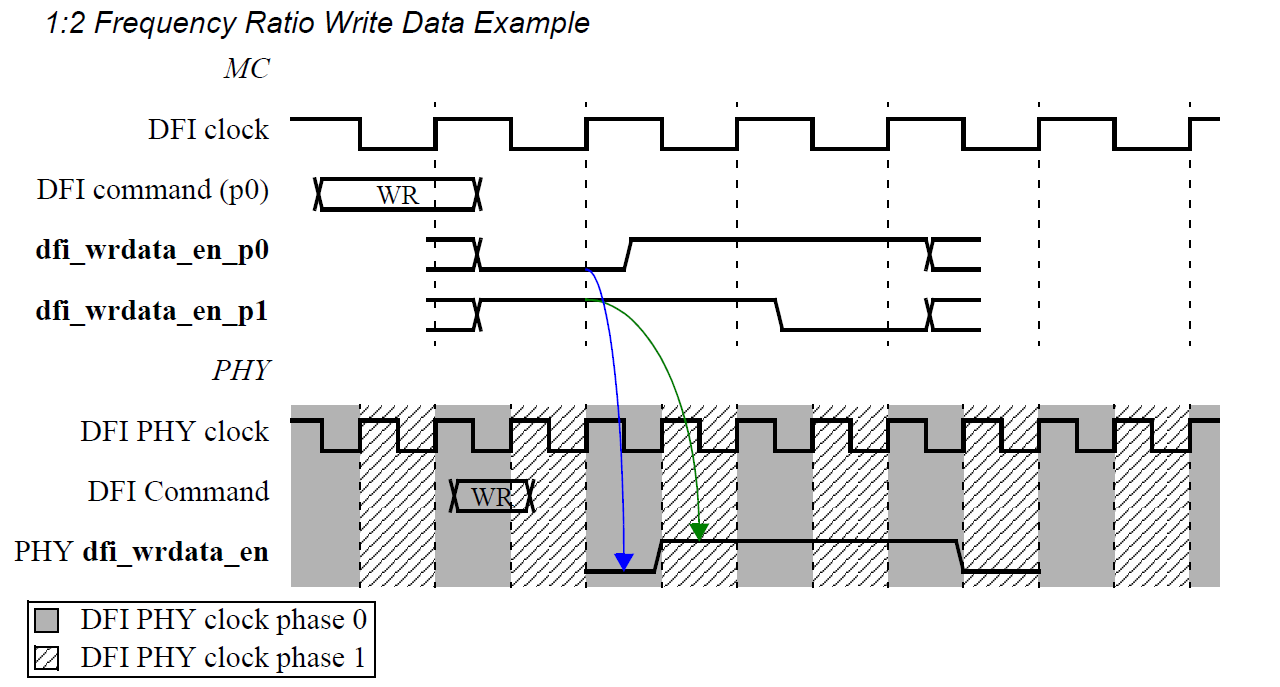

4.8.3 Write Data Interface in Frequency Ratio Systems

这个章节主要讨论在频率比系统(如1:2或1:4的MC到PHY频率比)中,写数据接口如何通过DFI协议进行管理。以下是详细的解释:

1. 写数据使能信号(dfi_wrdata_en_pN)

dfi_wrdata_en_pN信号表示在给定的时钟周期内,PHY接收到有效的dfi_wrdata数据。- 它的宽度定义了写操作的 “数据相位” 数量。也就是说,DFI写数据操作可以分为多个阶段,每个阶段在不同的时钟相位上进行。

- 在频率比系统中,由于MC和PHY的频率不同,这个信号需要被向量化(vectoring),也就是说,它会分解成多个信号,每个信号都对应一个DFI PHY时钟的相位。例如,在1:4频率比的系统中,

dfi_wrdata_en_pN可能被拆分为多个信号,如dfi_wrdata_en_p0、dfi_wrdata_en_p1、dfi_wrdata_en_p2、dfi_wrdata_en_p3,每个信号控制相应相位的数据。

2. 写数据总线宽度

- 在匹配频率的系统中(即MC和PHY的频率相同),DFI写数据总线的宽度通常是DRAM数据总线宽度的两倍。

- 在频率比系统中,DFI写数据总线宽度会根据频率比进行调整,确保在一个DFI时钟周期内可以发送所有内存需要的写数据。具体来说,如果频率比是1:2或1:4,DFI写数据总线的宽度会根据这个比例增加,以便在单个DFI时钟周期内传输完整的数据。

3. 写数据对齐

- 写数据必须按顺序对齐,即确保所有的数据片段(例如,多个数据字)按照从低到高的顺序排列。这种对齐确保了数据在多个时钟周期中被正确接收并传输。

4. tphy_wrlat 和 tphy_wrdata 时序参数

- tphy_wrlat:定义了从写命令发出到

dfi_wrdata_en_pN信号被激活之间的延迟。 - tphy_wrdata:定义了从

dfi_wrdata_en_pN信号被激活到数据实际驱动到dfi_wrdata_pN信号的延迟。 - 这些时序参数是以DFI PHY时钟为基准来定义的,并且它们是基于PHY如何解释数据的方式来进行测量的。

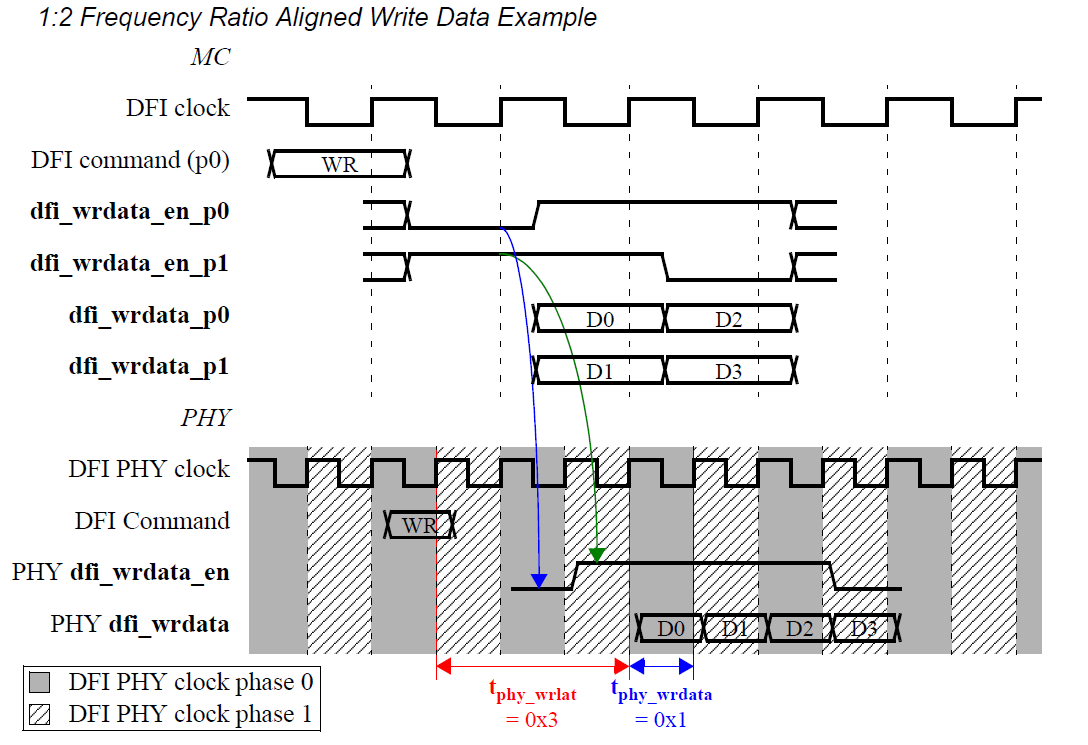

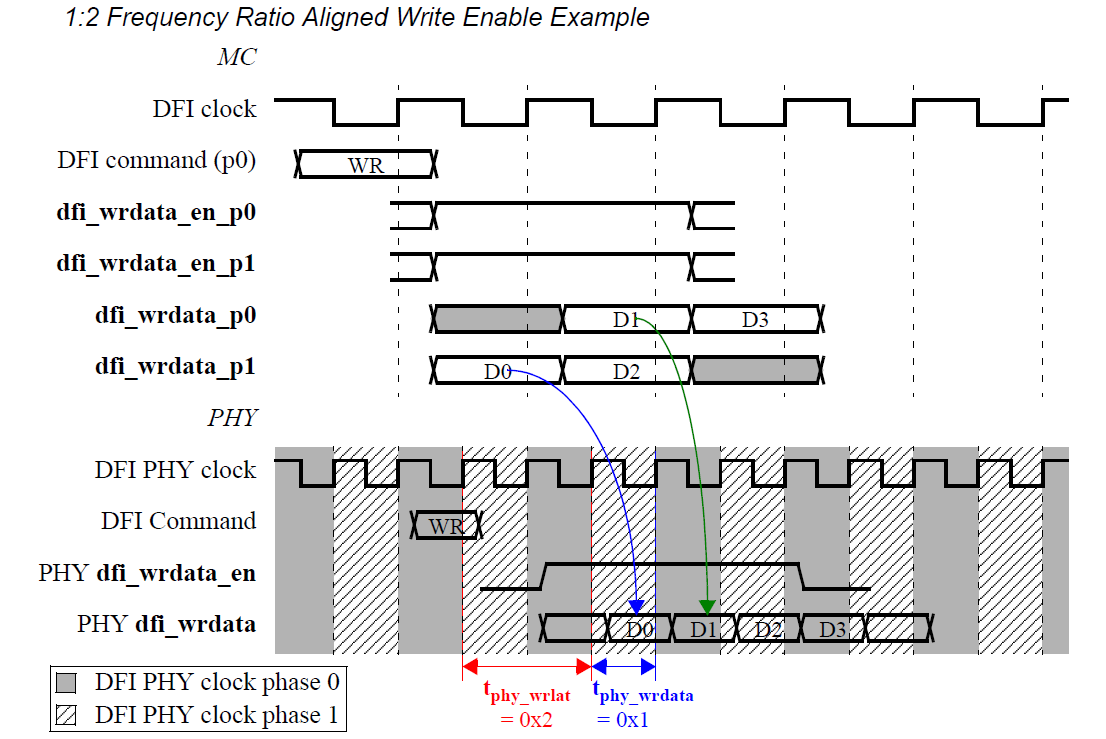

5. 时序图

- 图39展示了在1:2频率比系统中,向量化的

dfi_wrdata_en_pN信号是如何被PHY解释的。PHY时序仅用于说明目的。

- 图40展示了在数据对齐发送,但使能信号未对齐的情况下,PHY如何接收数据。

- 在图41中,使能信号是对齐发送的,但数据未对齐。MC将数据的第一拍发送到相位1的数据信号。为了实现命令与数据之间的正确关系,写数据必须以非对齐的方式发送。

4.8.4 Read Data Interface in Frequency Ratio Systems

这段内容讨论的是在频率比系统中,DFI(Data Flow Interface)协议中的读数据接口(read data interface)是如何工作的。具体来说,它描述了在不同的频率比(例如 1:2 或 1:4)系统中,如何使用 dfi_rddata 信号来传输数据,并规定了数据的返回顺序和有效信号的使用规则。以下是详细的逐步解释:

1. 读数据使能信号 (dfi_rddata_en_pN)

- 功能:

dfi_rddata_en_pN信号与写数据使能信号相似,它定义了从读命令到读数据之间的时钟周期数,并且其宽度决定了读取数据的相位数。 - 作用:通过这个信号,PHY(物理层接口)控制何时将数据发送给内存控制器(MC)。这信号的宽度决定了数据的“阶段数”(数据阶段)。

2. 数据的传输

- 数据传输:当数据准备好时,PHY会通过

dfi_rddata_wN总线发送读数据,并且会同时置位dfi_rddata_valid_wN信号,告诉内存控制器哪些总线包含有效数据。 - 信号的向量化:与读数据使能信号不同,读数据(

dfi_rddata)、有效数据(dfi_rddata_valid)和无效数据(dfi_rddata_invalid)信号是按 DFI 数据字后缀进行向量化的。也就是说,这些信号是以多个数据字的形式组织的。

3. 频率比系统中的数据总线划分

- 1:2 比率系统:在这种情况下,读数据总线被分为 2 个 DFI 数据字。例如,如果内存数据宽度是 32 位,那么 DFI 读数据总线会有 2 个 64 位的数据字。

- 1:4 比率系统:在 1:4 比率系统中,读数据总线被分为 4 个 DFI 数据字。此时,每个 DFI 数据字传输的是内存数据字(例如,一个 32 位的内存数据单元会被分配到多个 64 位的 DFI 数据字中)。

4. 数据返回顺序

- 滚动顺序:无论是 1:2 还是 1:4 的频率比系统,数据必须按滚动顺序返回。滚动顺序指的是返回数据时,必须按一定的顺序在不同的

dfi_rddata_wN总线上发送数据。这个顺序是为了保证数据传输的连续性和正确性。 - 举例:在 1:4 系统中,如果某次数据通过

dfi_rddata_w0和dfi_rddata_w1总线返回,下一次数据传输必须从dfi_rddata_w2总线开始,而不是从dfi_rddata_w0总线再次开始。 - 重要规则:每个数据传输必须确保在上一个数据传输的基础上,按顺序使用下一个数据字总线。例如,如果最后一次传输结束于

dfi_rddata_w2,那么下一次数据传输必须从dfi_rddata_w3开始。

5. 数据的合法性

- 合法顺序:如果读取的数据量小于 DFI 读数据总线的宽度(例如,数据量小于 128 位),那么只能在部分数据字总线中返回数据。例如,如果在 1:4 系统中,只返回了两个数据字,那么数据会通过

dfi_rddata_w2和dfi_rddata_w3总线传输。 - 非合法情况:不能只在

dfi_rddata_w0和dfi_rddata_w2总线返回数据,因为这样会破坏数据的滚动顺序。

6. 数据指针和初始化

- DFI 数据字指针:在初始化时,DFI 数据字指针会设置为 0,意味着第一次返回的读数据应该从

dfi_rddata_w0总线开始。 - 初始化时的重置:在一些特定操作(例如频率改变、数据训练或门控训练)之后,DFI 数据字指针可能需要重置。这通常是通过信号

dfi_init_start或其他信号(如dfi_rdlvl_en)来触发。

7. 频率比和数据传输

- 频率比影响:在频率比系统中,如果最小的数据传输量是 DFI 读数据总线宽度的整数倍,那么可以在所有的 DFI 数据字上同时返回数据,

dfi_rddata_valid_wN信号也会被同时驱动。 - 可选的 PHY 实现:某些PHY实现可能允许每次传输都在整个 DFI 数据总线上返回数据,而不考虑数据量。

8. 时序约束

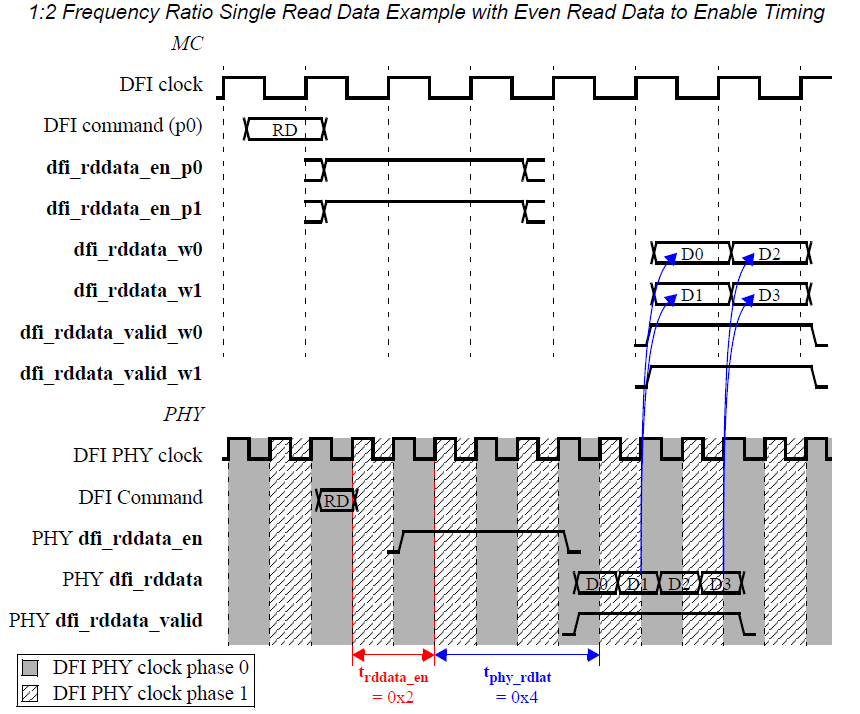

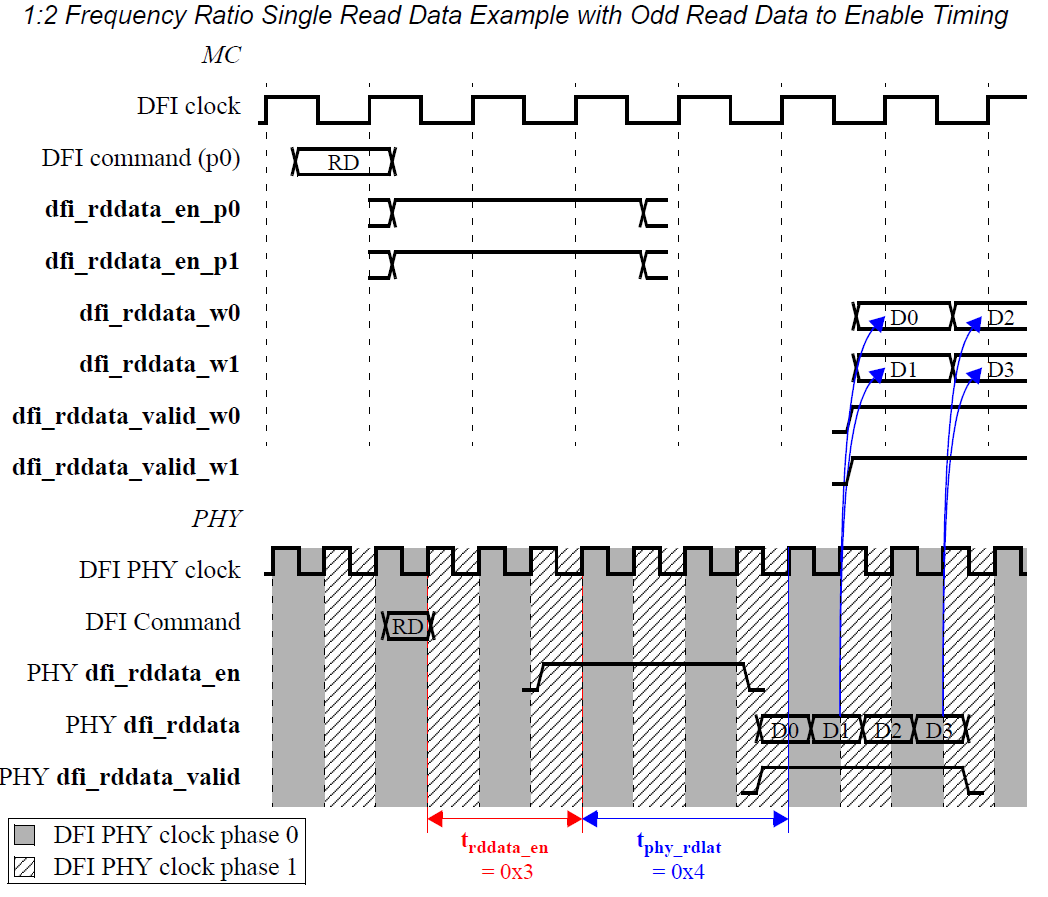

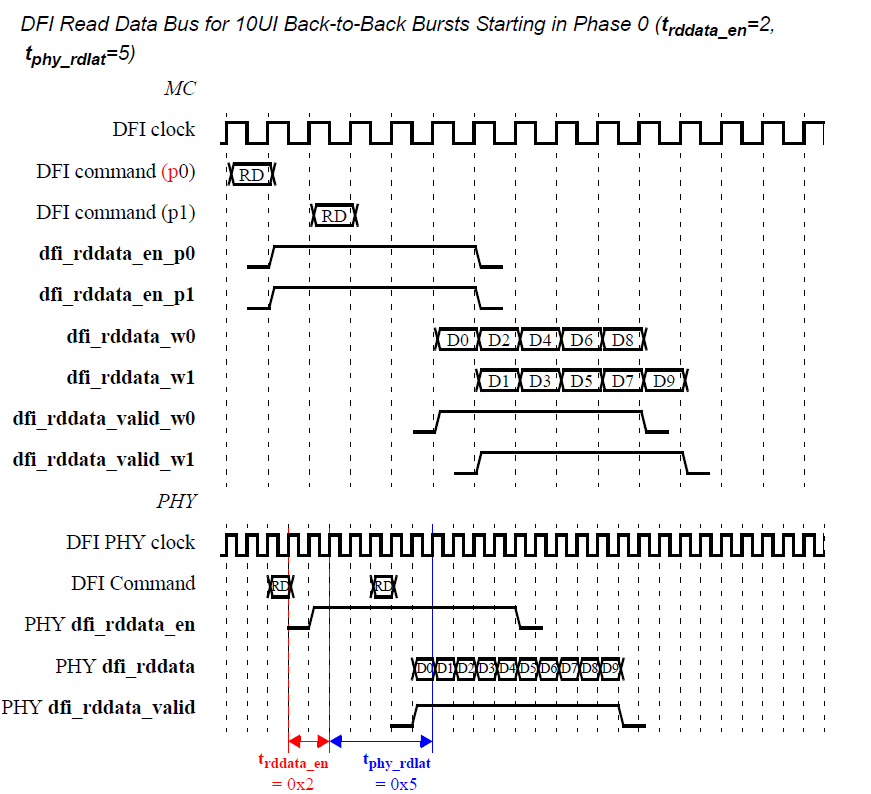

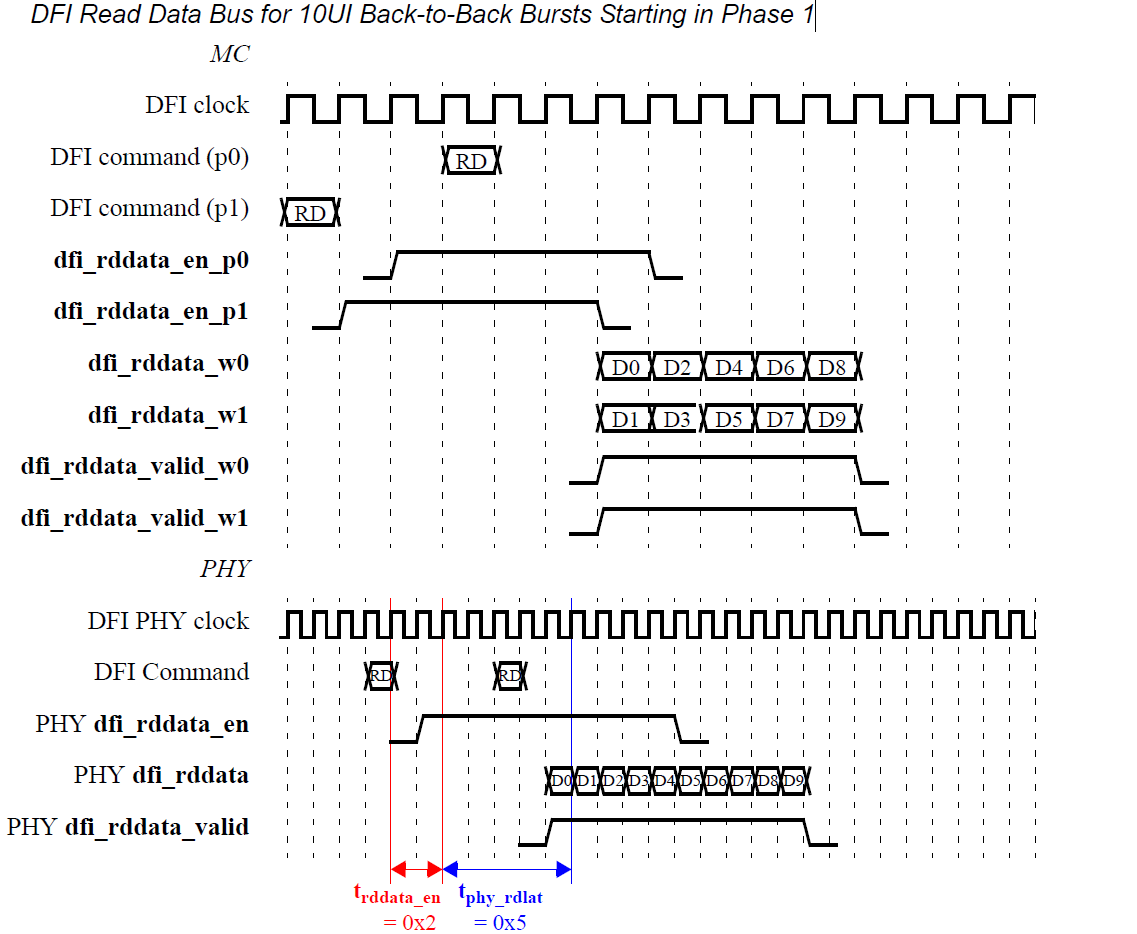

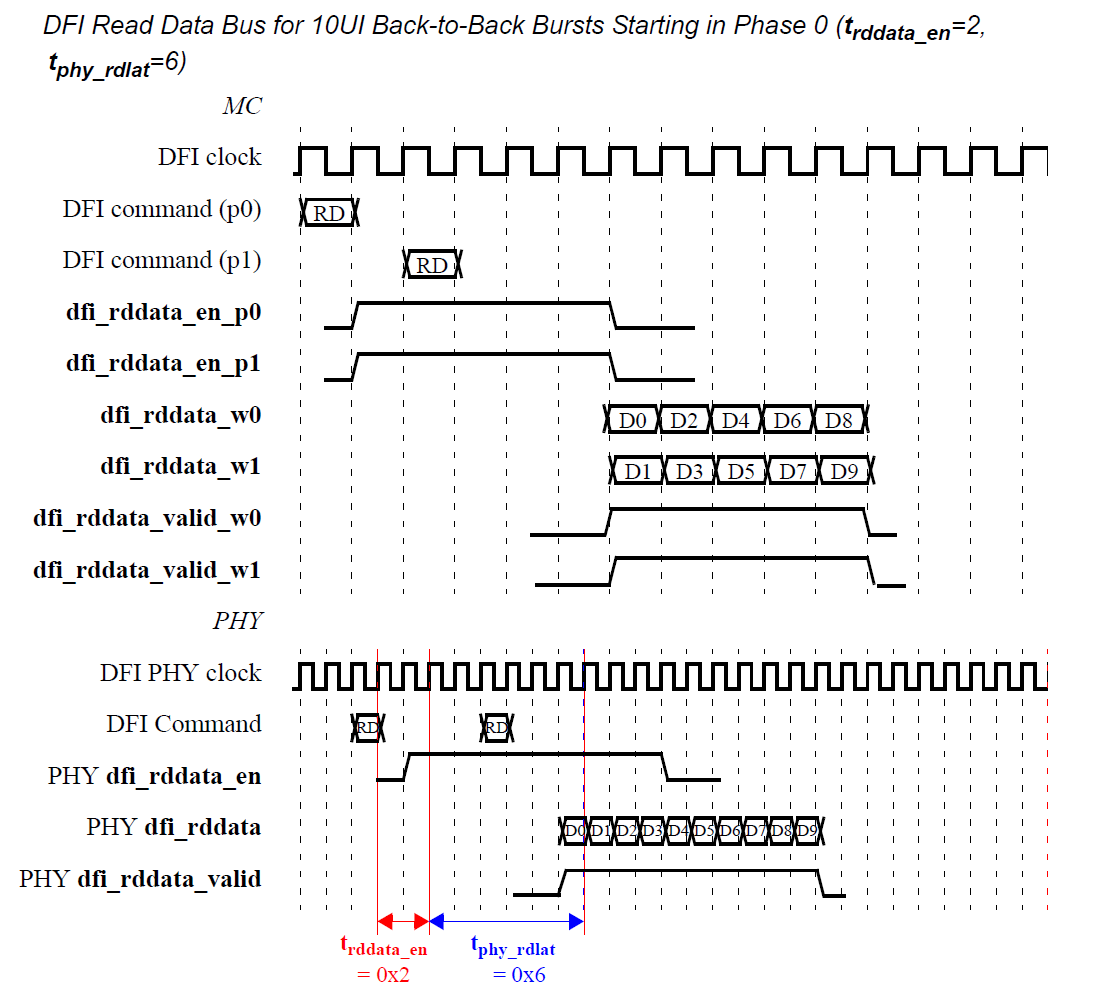

- 时序参数:

trddata_en和tphy_rdlat这两个时序参数在频率比系统中与匹配频率系统中一样适用。它们分别定义了从读命令到dfi_rddata_en_pN信号的延迟,以及从dfi_rddata_en_pN信号到数据通过dfi_rddata_wN总线返回的延迟。

9. 时序图

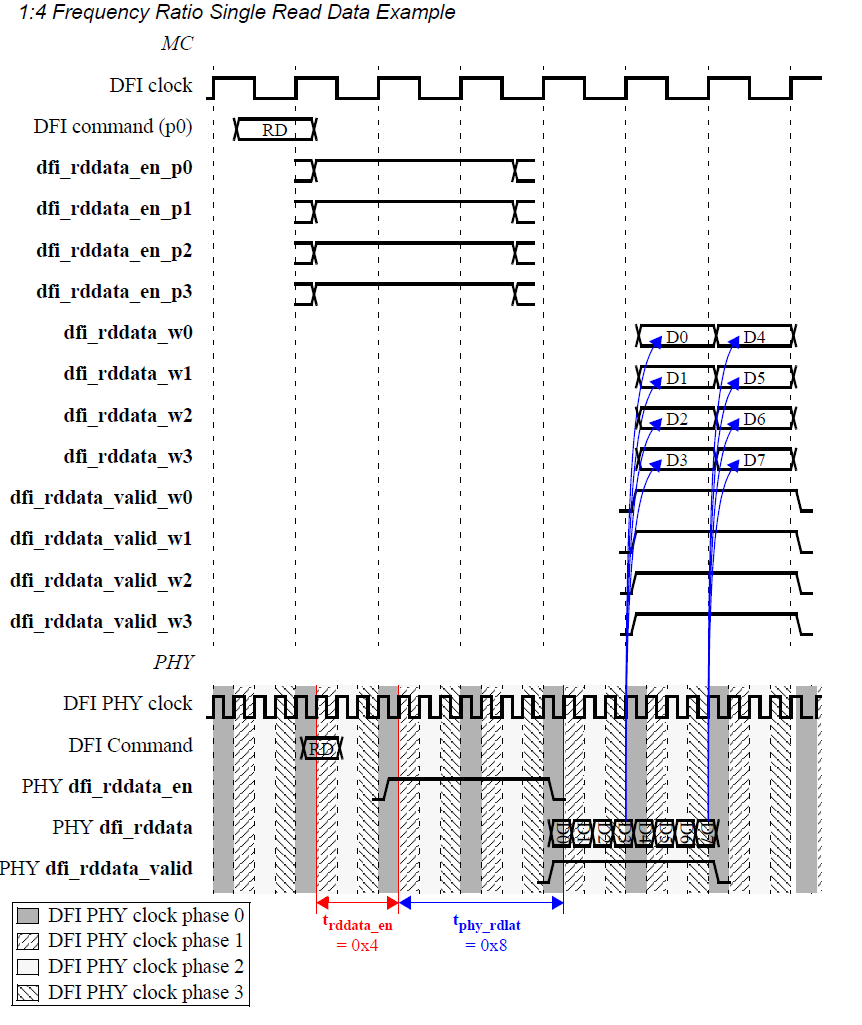

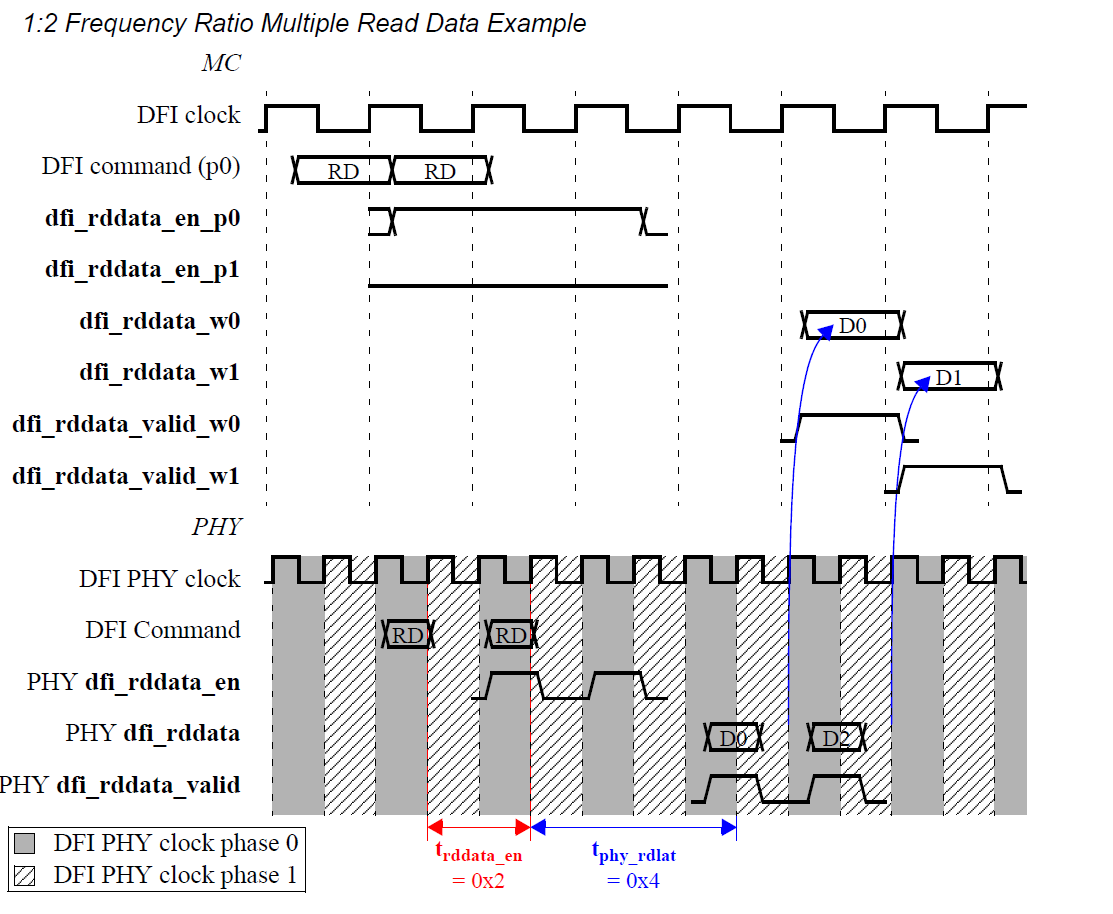

- 图 42 演示了在一个 1:2 频率比系统中,带有偶数值的

trddata_en时序参数的情况下,如何通过向量化的dfi_rddata_en_pN信号被 PHY 解释,并且在一个 DFI 时钟周期内返回所有 DFI 数据字。PHY 时序仅用于说明目的。

- 图 43 演示了在一个 1:2 频率比系统中,带有奇数值的

trddata_en时序参数的情况下,如何通过向量化的dfi_rddata_en_pN信号被 PHY 解释,并且在一个 DFI 时钟周期内返回所有 DFI 数据字。PHY 时序仅用于说明目的。

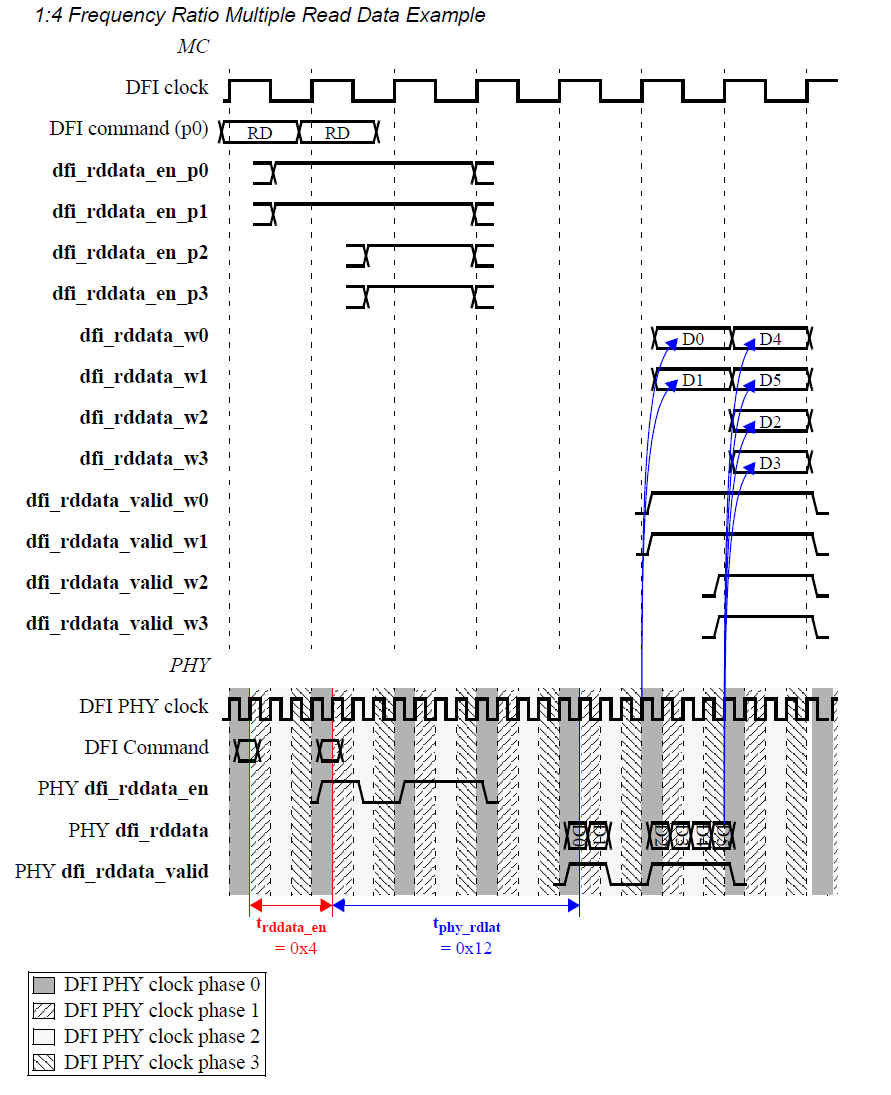

- 图 44 演示了在一个 1:4 频率比系统中,如何通过向量化的

dfi_rddata_en_pN信号被 PHY 解释,并且在一个 DFI 时钟周期内返回所有 DFI 数据字。PHY 时序仅用于说明目的。

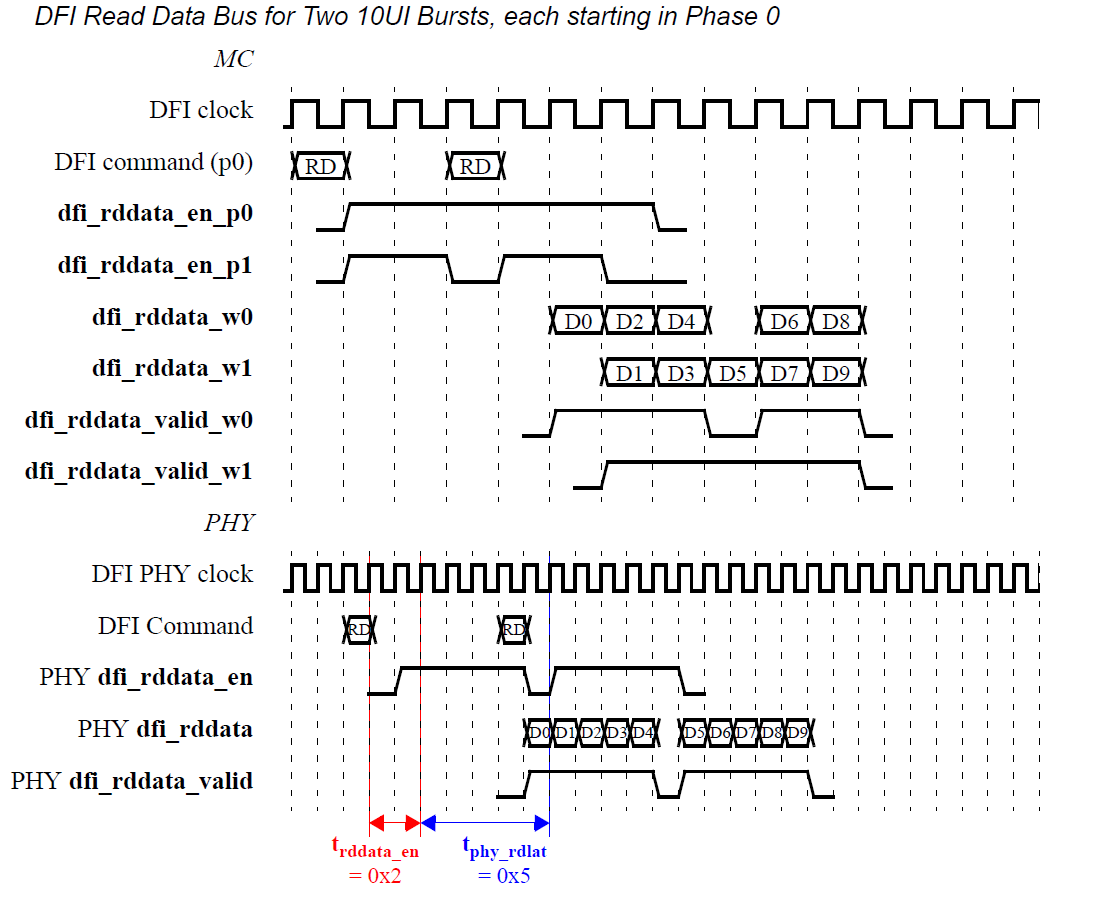

- 图 45 演示了每个命令返回一个单独的 DFI 数据字。第二个读命令的数据按照滚动顺序规则,通过

dfi_rddata_w1总线返回。PHY 时序仅用于说明目的。

- 与图 45 相似,图 46 展示了一个突发长度为 4 的读命令,随后是一个突发长度为 8 的读命令。根据滚动顺序规则,突发长度为 8 的读命令的数据从

dfi_rddata_w2总线开始返回。PHY 时序仅用于说明目的。

- 对于匹配频率系统,DFI 读数据总线的宽度通常是 DRAM 数据总线宽度的两倍。对于频率比系统,DFI 读数据总线的宽度与频率比成正比,以便将内存返回的所有读数据在一个 DFI 时钟周期内传送。读数据必须按照 DFI 数据字升序对齐进行传输。

4.8.4.1 DFI Read Data Rotation

在 频率比系统 中,如果一次读取的数据量不是 dfi_rddata 总线宽度的整数倍,系统必须严格遵守读取数据的轮换顺序规则。下面是这个章节的详细解释:

1. 读数据轮换规则

- 轮换顺序:在频率比系统中,读数据会根据 dfi_rddata_wN 总线返回,并且必须遵循 DFI 数据字的轮换顺序。例如,对于 1:2 频率比系统,如果在一个 DFI 时钟周期内数据从 dfi_rddata_w0 总线返回,那么下一个事务的数据必须从 dfi_rddata_w1 总线开始返回,而不管返回的数据量是多少。

- 滚动顺序:不管是下一次数据传输发生在下一个 DFI 时钟周期,还是发生在几个时钟周期之后,都必须遵循这个顺序。

2. 特殊情况

- 非整数倍数据传输:在某些情况下,读取的数据量可能不是频率比的整数倍。例如,在 4:1 频率比系统 中,一个 4 字的数据突发传输需要使用 2 个 DFI 数据字。所以,下一次访问可能会从 dfi_rddata_w2 总线开始,而不是从 dfi_rddata_w0 总线开始。

3. 示意图说明

- 为了简单说明,章节提到了一些示意图(如图 4.6 PHY Update),这些图展示了在 1:2 频率比系统下,如何传输 2 个数据突发,其中每个突发会延长一个 DRAM 时钟周期。图 4.6 描述了在读取数据字数不是频率比的倍数时,PHY 和控制器的要求。

4. 频率比不为整数倍的突发传输

- 大多数 DFI 系统不需要支持数据传输字数不是频率比整数倍的突发传输。然而,如果一个系统确实需要支持这种突发传输,PHY 必须遵守上述的 轮换顺序规则 来传输数据。

- 同时,MC 必须能够正确捕获这些数据,并将其与对应的读命令关联起来。

5. 时序图

- 图47

- 图48

- 图49

- 图50

4.8.4.1.1 Read Data Resynchronization

1. 读数据同步

- 在读数据轮换顺序规则适用时,MC 和 PHY 必须保持同步,才能正确解释读取数据的顺序。如果发生了可能导致读取数据同步丢失的情况,系统需要具备重新同步的机制。

2. 重新同步机制

- 何时需要重新同步:重新同步通常在发生了 训练 或 错误报告 等情况时触发。这时,MC 和 PHY 必须通过重新同步来确保数据正确。

- 如何重新同步:

- 当 dfi_ctrlupd_req 或 dfi_phyupd_ack 信号被触发时,MC 和 PHY 都应该重置读取数据顺序。

- 在这之后,无论上次数据字位于哪个总线位置,接下来的读取数据都会从 dfi_rddata_w0 总线开始传输。

3. 具体实施

- 这种同步机制保证了即使在频率比系统中发生了错误或训练等情况,设备仍然能够重新同步并继续正常工作。

本文链接: https://talent-tudou.github.io/2024/12/28/DFI/DFI Spec-Frequency Ratios Across the DFI/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!