7.1 HDR Write/Read Timing(写/读时序)

这一节描述的是控制器与 PHY(物理层)之间的所有时序细节,特别是 读写操作时序波形,包括以下几类信号:

- DFI 信号(dfi_):用于控制读写操作的数据总线信号。

- PUB/PHY 接口信号:

- ctl_clk:控制信号时钟。

- ddr_clk:DDR 时钟。

- **ctl_、phy_**:控制和 PHY 相关的信号。

- SDRAM 信号:

- ck/ck_n:时钟和反相时钟信号。

- cmd:命令信号,控制读写等操作。

- dqs/dqs_n:数据时钟信号。

- dq:数据总线信号。

通常情况下,这些波形图展示的是一些典型的信号。例如,ctl_ac[3:0] 表示与特定 SDRAM 命令相关的所有地址/命令信号。

时序概念

两个命令周期:在一个控制器时钟周期内可以有两个命令。[CMD1:CMD0] 表示这两个命令:

- CMD0:第一个(偶数)命令,通常在第一个时钟周期(SDR 时钟)发出。

- CMD1:第二个(奇数)命令,通常在第二个时钟周期发出。

需要注意的是,通常情况下,只有一个命令有效,另一个是 NOP(No Operation,空操作)。

不同配置下的时序波形

读写波形会根据 PHY 配置 和 SDRAM 延迟 的不同而有所不同。对于 DDR3 和 DDR4 模式,波形大多数是相同的,但有少数情况下会有差异。通常,波形会显示 DDR3 时序,而 DDR4 时序部分会显示在波形的底部,专门针对那些在 DDR4 模式下有不同时序的信号。

奇偶延迟对时序的影响

- 写延迟(Write Latency,WL) 和 读延迟(Read Latency,RL) 会影响时序。

- 奇数延迟和偶数延迟:写延迟和读延迟通常是 偶数 或 奇数,因此会有不同的时序波形。

- 对于每种类型的访问,会给出不同的波形示例:

- WL/RL = 偶数:当写/读命令从控制器发出时,延迟为偶数时。

- WL/RL = 奇数:当写/读命令从控制器发出时,延迟为奇数时。

- 命令周期0 和 命令周期1:

- 如果写/读命令从周期 0 发出,或者周期 1 发出,波形会有所不同。

时序波形与延迟

- 每个 RWL(Read/Write Latency) 的延迟可以通过调整控制信号的时序来推导,具体是通过将控制信号(例如 ctl_oe、ctl_ds_en、ctl_qs_en 和 ctl_d)的时序相对于 ctl_cmd 信号进行偏移。这个偏移量是

(RWL - 6 或 5) / 2控制器时钟周期。- 如果 RWL 为偶数或奇数,则对应使用 6 或 5 的波形,来根据实际的延迟设置调整时序。

延迟公式

- 对于 DDR3/4:

- 写延迟(WL) = CAS 写延迟(CWL) + 附加延迟(AL)

- 读延迟(RL) = CAS 延迟(CL) + 附加延迟(AL)

不同模式下的时序

- 升降模式(rise-to-fall mode):在此模式下,控制信号从升沿到降沿传输,时序图显示的是这种模式下的波形。

- 升升模式(rise-to-rise mode):当 rr_mode 设置为 ‘1’ 时,控制信号从升沿到升沿传输。与升降模式的主要区别是,PHY 命令和写延迟、PHY 读延迟都会增加 半个控制器时钟周期。

- 这个配置是在

DSGCR寄存器中(0x24)

四种时序情况

- WL/RL = 偶数,并且控制器的写/读命令出现在 周期0。

- WL/RL = 奇数,并且控制器的写/读命令出现在 周期0。

- WL/RL = 偶数,并且控制器的写/读命令出现在 周期1。

- WL/RL = 奇数,并且控制器的写命令出现在 周期1。

在每种情况下,如何驱动控制信号(例如 ctl_ds_en、ctl_oe、ctl_qs_en 和 ctl_d)来实现正确的前导和延迟是非常重要的。特别地,ctl_qs_en 信号在读取时如何驱动,以确保 DQS(数据时钟)门控 正确。

7.1.1 Write Timing(写时序)

背景

这部分介绍了 DFI 写时序,特别是对于 控制器偶数命令(CMD0),写延迟(Write Latency,WL)为8 和 突发长度(Burst Length,BL)为8 的情况。DFI 主要涉及数据传输的时序信号,这些信号控制了从控制器到 PHY 的数据写入过程。

DFI 写时序图(Figure 7-1)

图 7-1 展示了 DFI 写时序,其中包括以下主要参数:

- 控制器偶数命令(CMD0):在控制器中有两个命令周期,偶数命令通常是第一个命令,奇数命令通常是第二个命令。这里讨论的是偶数命令(CMD0)。

- 写延迟(Write Latency,WL)= 8:写延迟决定了从写命令发出到实际写数据传输之间的延迟周期数。

- 突发长度(Burst Length,BL)= 8:表示一次连续传输的数据单元的长度为 8。

tphy_wrlat(PHY 写延迟)

tphy_wrlat 表示 DFI 写命令与 DFI 写数据使能信号(dfi_wrdata_en)之间的间隔。这个间隔的单位是 SDRAM 时钟周期(tCK)。

根据图 7-1,tphy_wrlat 的间隔为 (WL – 2) tCK。这意味着,如果写延迟(WL)为 8,那么 tphy_wrlat = 6 tCK(即 6 个时钟周期)。

- 公式推导:tphy_wrlat = WL - 2 = 8 - 2 = 6 tCK

也就是说,在写延迟为 8 的情况下,DFI 写命令和写数据使能信号之间的间隔为 6 个时钟周期。

控制器写数据(dfi_wrdata)和写数据使能(dfi_wrdata_en)

- DFI 控制器在驱动写数据使能信号(dfi_wrdata_en)后,会在 1 个时钟周期 后驱动实际的数据(dfi_wrdata)。这意味着数据与使能信号之间的关系是:

- 写数据使能信号和写数据本身的时序是相同的,即它们之间是紧密相连的,写数据会紧随写数据使能信号发送。

DFI 写数据掩码(dfi_wrdata_mask)

- 由于写数据掩码信号(dfi_wrdata_mask)的时序与写数据(dfi_wrdata)的时序是相同的,因此在时序图中没有单独显示。换句话说,掩码信号的行为与数据本身完全同步,它的作用是标记哪些数据有效,哪些数据无效。

时序模式:Rise-to-Rise 与 Rise-to-Fall

- Rise-to-Rise 模式:这是图示中的默认模式,表示信号从上升沿到上升沿进行传输。这意味着在一个时钟周期内,信号的变化发生在时钟的上升沿。

- Rise-to-Fall 模式:这是一种对时序要求稍微不同的模式,表示信号从上升沿到下降沿进行传输。在这种模式下,DFI 接口的时序要求与 Rise-to-Rise 模式相同,唯一的区别是:

- PHY 延迟会减少 1 个时钟周期(tCK)。这意味着在 Rise-to-Fall 模式下,PHY 的写延迟会比 Rise-to-Rise 模式快 1 个时钟周期。

7.1.2 Read Timing

背景

在 DFI 读时序中,主要涉及两种变量:

- trddata_en:表示 DFI 读命令(dfi_rdcmd)和 DFI 读数据使能信号(dfi_rddata_en)之间的时间间隔,通常表示为 (RL – 4) tCK。其中,RL 是读延迟(Read Latency),tCK 是时钟周期(SDRAM 时钟周期)。

- tphy_rdlat:表示 DFI 读数据使能信号(dfi_rddata_en)和 DFI 读数据有效信号(dfi_valid)之间的时间间隔,通常在时序图中给定一个常数值(例如 18 个时钟周期)。

时序分析

- DFI 读时序的主要步骤:

- trddata_en 的计算是基于 RL(读延迟)。如果 RL = 8,那么 trddata_en = RL – 4 = 8 – 4 = 4 tCK,也就是说 dfi_rddata_en 信号和 dfi_rdcmd 信号之间的间隔为 4 个时钟周期。

- tphy_rdlat 是指从 dfi_rddata_en 到 dfi_valid 之间的间隔。在图中示例,tphy_rdlat = 18 tCK。这是 PHY 内部延迟的一个常数值,代表数据从 PHY 进入 控制器并且变为有效的时间。

时序模式:Rise-to-Rise 和 Rise-to-Fall

- Rise-to-Rise 模式:表示信号的上升沿到下一个周期的上升沿。所有描述的时序图默认是 Rise-to-Rise 模式。

- Rise-to-Fall 模式:表示信号从上升沿到下降沿的变化。在 Rise-to-Fall 模式下,PHY 内部的延迟会减少 1 个时钟周期(tCK)。所以,在该模式下的时序图与 Rise-to-Rise 模式相比,命令路径和数据路径的延迟会更短。

突发长度(Burst Length,BL)影响

- 突发长度为 8 和 突发长度为 4 的时序差异:

- Burst Length = 8 时,时序中会有更多的数据位宽和数据使能信号,而 Burst Length = 4 时,数据位宽和数据使能信号会减半。

- 但 trddata_en 和 tphy_rdlat 的计算方法是相同的。

偶/奇命令和偶/奇读延迟的不同

- 偶命令和偶读延迟:这是最常见的组合,通常时序会比较简单。

- 奇命令和偶读延迟:当 命令周期 为奇数时,时序会发生一些变化,通常会延迟一个时钟周期。

- 偶命令和奇读延迟:当 读延迟 为奇数时,trddata_en 的值会增加或减少 1 个时钟周期。例如,在 图7-6 中,命令周期 是偶数,而 读延迟 是奇数,时序需要做适当的偏移调整。

- 奇命令和奇读延迟:类似地,trddata_en 需要调整以适应时序要求。

时序图和数据位宽

- Burst Length = 8 时的数据时序和 Burst Length = 4 时类似,唯一的区别是 数据位宽 和 读数据使能信号宽度,对于 Burst Length = 4,这些宽度会减半。

7.2 Controller SDR Write/Read Timing

背景

在 控制器 SDR 模式下,控制器运行的时钟频率是 PHY 时钟频率的两倍。虽然控制器时钟频率更高,但 PHY 和几乎所有的 PUB 逻辑仍然运行在 HDR 模式下。HDR 模式的时序在文档的其他部分已经详细描述,而 控制器 SDR 模式的时序则是将 SDR DFI 命令(来自控制器)转换为 HDR DFI 命令(到 PHY),并且这些转换后的命令具有与 HDR 模式相同的时序。

- SDR 模式:控制器在这种模式下运行,时钟频率为 PHY 的两倍。

- HDR 模式:PHY 和 PUB 逻辑依然运行在 HDR 模式时,控制器 SDR 模式的 DFI 命令会被转换成与 HDR 模式相同的时序。

7.2.1 Controller SDR Write Timing

在这一部分,介绍了 控制器 SDR 写时序,特别是在 写延迟(Write Latency,WL)为 8 和 突发长度(Burst Length,BL)为 8 的情况下,DFI 写时序的详细描述。

DFI SDR 写时序

- tphy_wrlat(PHY 写延迟)是 DFI 写命令和 DFI 写数据使能信号(dfi_wrdata_en)之间的间隔。这个间隔的单位是 SDRAM 时钟周期(tCK)。

- 具体来说,tphy_wrlat 的计算方式为:

- tphy_wrlat = (WL - 2) tCK

- 如果写延迟(WL)为 8,那么 tphy_wrlat = 6 tCK,或者 3 tCTLCLK。也就是说,在 WL = 8 时,tphy_wrlat 等于 6 个时钟周期(tCK),或者 3 个控制器时钟周期(tCTLCLK)。

DFI 写数据和写数据使能

- DFI 控制器会在驱动写数据使能信号(dfi_wrdata_en)后 1 个时钟周期,驱动实际的写数据(dfi_wrdata)。这意味着数据与使能信号之间的关系是:

- 写数据使能信号与写数据在时序上是紧密同步的。

- DFI 写数据掩码(dfi_wrdata_mask)的时序与写数据的时序相同,因此在图中没有单独展示。

时序模式:Rise-to-Rise 与 Rise-to-Fall

- Rise-to-Rise 模式:表示信号的变化从一个时钟周期的上升沿到下一个时钟周期的上升沿。这是默认的时序模式。

- Rise-to-Fall 模式:表示信号变化从上升沿到下降沿。对于 Rise-to-Fall 模式,在 DFI 接口的要求相同,唯一的区别是:

- PHY 延迟会减少 1 个时钟周期(tCK),意味着在这种模式下,PHY 的写延迟比 Rise-to-Rise 模式快。

突发长度(Burst Length,BL)的影响

- 突发长度 4 和 8 的时序非常相似。主要的区别是:

- 对于 突发长度为 4,写数据和写数据使能信号的位宽会比 突发长度为 8 时的位宽小一半。因此,写时序的波形会保持一致,只是数据位宽不同。

写延迟的奇偶性(Odd/Even Write Latency)

- SDR 模式下没有奇数命令周期,因为 DFI 时钟频率与 DRAM 时钟频率相同,所以在时序图中只展示了 偶数写延迟的情况。

- 如果写延迟为奇数(Odd Write Latency),则 tphy_wrlat 会增加或减少 1 个时钟周期,这取决于写延迟的奇偶性。

7.2.2 Controller SDR Read Timing

背景

在 SDR 模式下,控制器的时钟频率和 DRAM 时钟频率相同,因此 DFI 时钟频率等于 DRAM 时钟频率,并且没有奇数命令周期。描述的时序图是基于 读延迟(Read Latency,RL)为 8 和 突发长度(Burst Length,BL)为 8 的情况。时序中的关键变量包括:

- trddata_en:这是 DFI 读命令 和 DFI 读数据使能信号(dfi_rddata_en) 之间的间隔。

- tphy_rdlat:这是 DFI 读数据使能信号(dfi_rddata_en) 和 DFI 读数据有效信号(dfi_valid) 之间的间隔。

DFI SDR 读时序

关键变量:

trddata_en:这个值表示 DFI 读命令 和 DFI 读数据使能信号 之间的时钟周期数。它的计算公式为:

- trddata_en = (RL – 4) tCK

- 对于 RL = 8 的情况,trddata_en = 4 tCK。

这意味着,DFI 读命令 和 DFI 读数据使能信号 之间的间隔为 4 个时钟周期(tCK)。

tphy_rdlat:这个值表示 DFI 读数据使能信号 和 DFI 读数据有效信号 之间的间隔。对于 RL = 8,在时序图中,tphy_rdlat = 18 tCK。

也就是说,DFI 读数据有效信号 的有效时间会在 DFI 读数据使能信号 后 18 个时钟周期(tCK)有效。

时序模式:Rise-to-Rise 和 Rise-to-Fall

- Rise-to-Rise 模式:表示信号从一个时钟周期的上升沿到下一个时钟周期的上升沿。这是默认的时序模式。

- Rise-to-Fall 模式:表示信号变化从上升沿到下降沿。在 Rise-to-Fall 模式下,PHY 延迟会减少 1 个时钟周期(tCK),意味着命令路径和读数据路径的延迟会比 Rise-to-Rise 模式快 1 个时钟周期(tCK)。

突发长度(Burst Length,BL)的影响

- 突发长度为 8 和 突发长度为 4时的时序图非常相似,主要的区别在于:

- 对于 突发长度为 4,数据位宽会比 突发长度为 8 时小一半,即写数据使能信号的宽度也只有 突发长度为 8 时的一半。

奇偶读延迟(Odd/Even Read Latency)

- SDR 模式下没有奇数命令周期,因为 DFI 时钟频率与 DRAM 时钟频率相同。时序图中只展示了 偶数读延迟的情况。

- 如果 读延迟为 奇数(Odd Read Latency),则 trddata_en 会增加或减少 1 个时钟周期(tCK),从而调整时序。

7.3 PDA Mode Timing 解析

PDA Mode 概述

PDA(Precharge Delay Adjustment)模式是 DDR 控制器用来调整 预充电延迟(Precharge Delay)的特殊模式。一旦任意一个 rank(内存通道)进入 PDA 模式,控制器只能执行特定的命令,如 MRS(Mode Register Set)或 DES(Destructive Enable)命令。进入和退出 PDA 模式时,必须满足特定的时序要求,以确保 内存控制器、PHY 以及 内存的状态同步。

时序要求解析

1. 进入或退出 PDA 模式的等待时间

- 当进入或退出 PDA 模式时,必须有一个等待时间。这个等待时间是:

$$

\text{Wait time} = 2 \times \left( 6 + \left( \frac{WL - 4}{2} + 14 \right) + 1 + \text{PIPE_MCTL2DFI} + \text{PIPE_DFI2PHY} \right) \times t_{CK}

$$

其中:

- WL 是写延迟(Write Latency),它会影响等待时间的计算。

- PIPE_MCTL2DFI 和 PIPE_DFI2PHY 是内部的管道延迟,分别表示从 内存控制器 到 DFI 接口 和从 DFI 接口 到 PHY 的延迟。

该等待时间的作用是确保 内存控制器 的状态、PHY 的状态和内存的状态能够正确同步。

- 应用场景:

- 当 MRS 命令被发送进入 PDA 模式时,必须等待这个时序,确保内部状态完成初始化。

- 当 MRS 命令用于退出 PDA 模式时,同样需要等待这段时间,然后才能发出任何非 PDA 模式命令。

2. 调整写延迟以满足 tPDA_S

- WLSL(Write Latency Shift Level) 是一个调整的写延迟。在 PDA 模式下,PUB(内存控制器逻辑)会将 WLSL 调整为 -2,这是为了确保能够满足 tPDA_S。这意味着写延迟在进入 PDA 模式后会被减少 2 个时钟周期(tCK),以适应该模式的要求。

- tPDA_S 是一个时序约束,确保在 PDA 模式下写命令能够正确地执行。它通常是指控制器给定的一个周期,在此周期内,写命令需要被执行。

3. 调整 DQS 信号以满足 tPDA_H

- tPDA_H 是另一个时序约束,表示数据采样时机的延迟。在 PDA 模式下,控制器需要驱动额外的 DQS(Data Strobe)信号切换,以满足 tPDA_H 的要求。DQS 是数据总线上的一个信号,用于同步数据的读取和写入操作。

4. PBA Mode 说明

- PBA 模式(Precharge Bypass Adjustment)与 PDA 模式类似,PUB(内存控制器的逻辑)为两者提供相同的控制逻辑。因此,进入和退出 PBA 模式时,同样需要遵守上述的等待时间和时序要求。

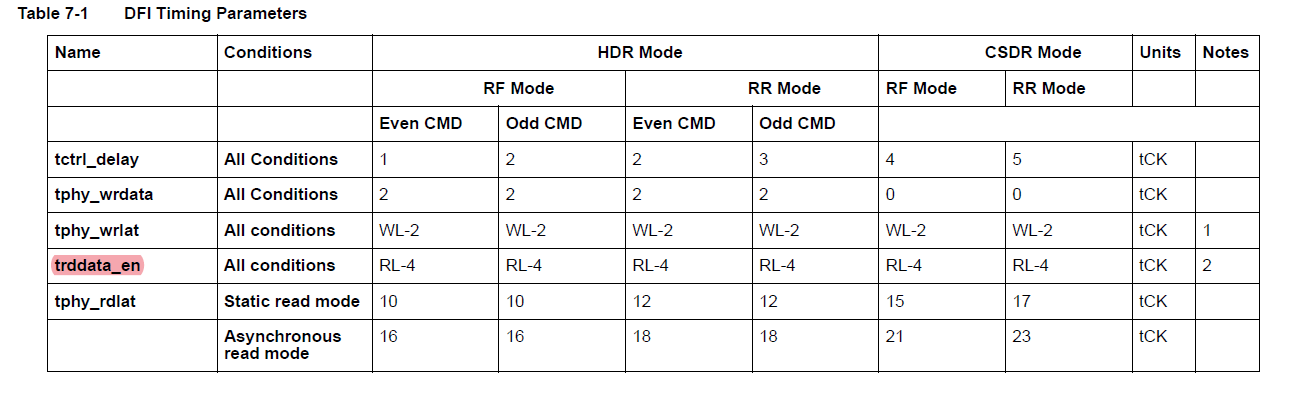

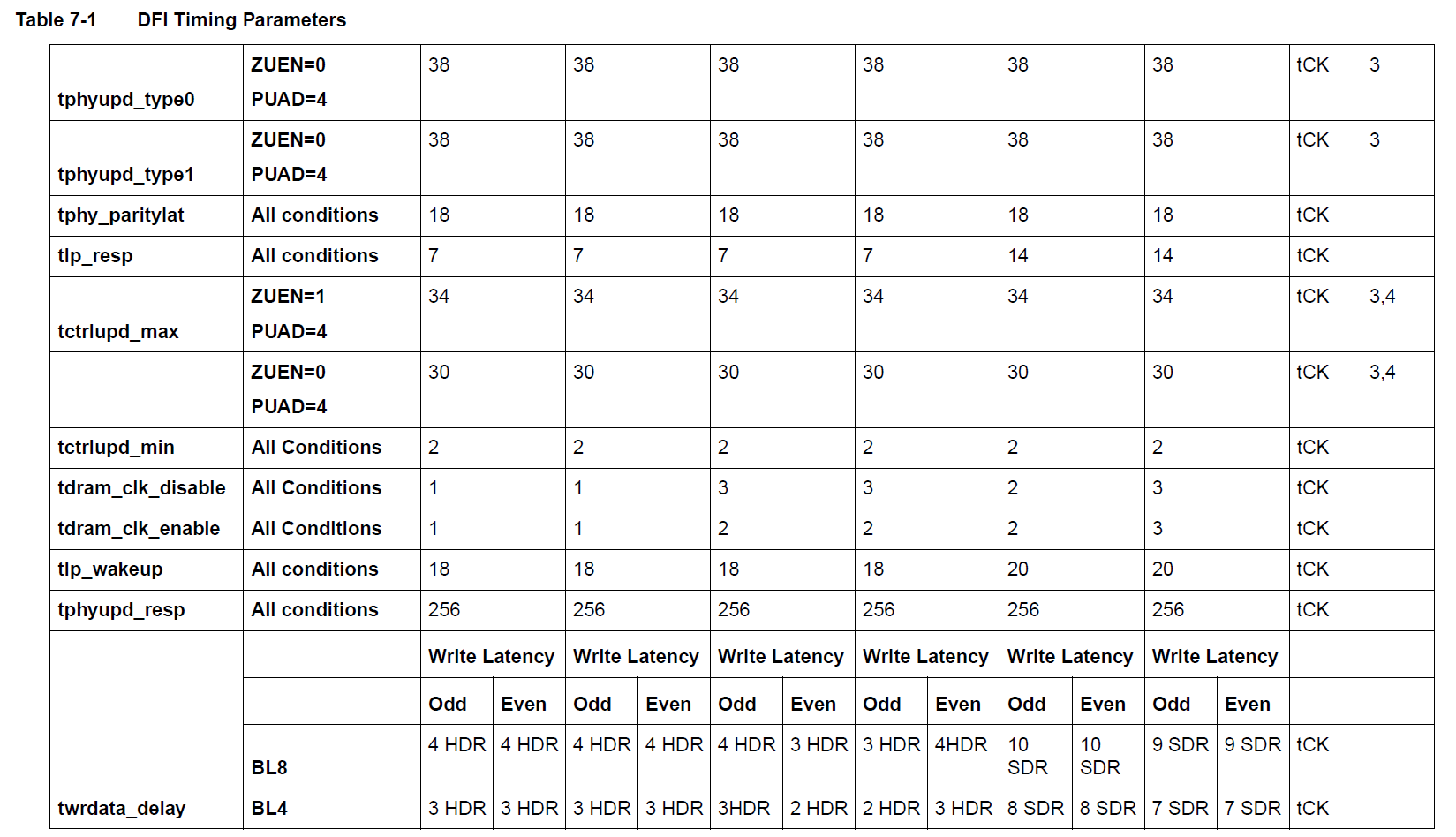

7.4 DFI 时序参数

表 7-1 给出了一个特定、最小设计的 DFI 参数。这些设计准则假设了以下条件:

测量模式:

- Rise-to-fall mode(RF模式):即从信号上升到下降时的时间。

- Rise-to-rise mode(RR模式):即从信号上升到下一个上升沿时的时间。

这些测量是没有启用任何 DFI 管道阶段(即没有内部缓冲)的情况下进行的。

无异步延迟:

- 假设 PHY 和 I/O 中没有异步延迟。通常,异步延迟指的是信号传播过程中由于不同模块或板卡上的不同时钟域造成的延迟。

零包/板载飞行时间:

- 假设包和板之间的信号传播延迟为零,这在理论上简化了时序分析。实际上,信号在 PCB(印刷电路板)上传播会有一定的延迟。

写入和命令延迟测量:

- 写入和命令延迟是从 ctl_clk(控制器时钟) 的边缘开始测量的,该时钟边缘用于捕获控制器中的命令或数据。这通常是系统中的主时钟信号。

读取延迟:

- 读取延迟的测量取决于 读数据时钟(DQS) 与控制器时钟的对齐方式。具体来说,读取延迟被测量到 ctl_clk 边缘,此时 SoC(系统芯片) 可以用来从 IP(内存接口模块) 捕获读数据。

- 最佳对齐是指读取数据时钟与控制器时钟之间的对齐达到最优时,读取延迟最短。

读取模式

- 静态读取模式:

- 在 PGCR3.RDMODE = 01 和 DXnGCR0.RDDLY/DXnGCR7.X4RDDLY = 1 的情况下工作。这些设置用于控制读取的时序和延迟,特别是在 内存控制器 的参数配置时。

- PGCR3.PRFBYP = 1 表示启用 预读 模式,即提前准备数据,减少访问延迟。

- 异步读取模式:

- 当 PGCR3.RDMODE = 00 且 PGCR3.PRFBYP = 0 时启用。异步模式通常指内存控制器不与外部时钟同步工作,读取延迟会更高且不可预测。

延迟四舍五入

- 分数延迟会四舍五入到下一个整数。这意味着在计算 PHY 延迟 时,如果得到的延迟是一个小数,它将向上取整,以简化设计中的实际实现。此举有助于减少时序分析的复杂性,但可能会导致系统时序的微小调整。

注意事项

1. Write Latency (WL) 和 Read Latency (RL)

这部分解释了 WL(写延迟) 和 RL(读延迟) 的定义及其计算方法,具体说明了不同类型的 SDRAM 的计算公式:

WL(写延迟):

- DDR4:WL = (CAS 写延迟(CWL) + 加法延迟(AL) + CA 奇偶校验延迟(PL) + RDIMM/LRDIMM 可编程命令延迟加法器)。

- DDR3:WL = (CAS 写延迟 + 加法延迟)。

- LPDDR3/2:WL = (DRAM 写延迟 + 1)。

WL 是从控制器发出写命令到数据被写入内存的时间延迟。在不同的内存类型中,计算方法会有所不同。例如,DDR4 的 WL 需要考虑 CAS 写延迟、加法延迟、CA 奇偶校验延迟,以及 RDIMM/LRDIMM(即内存模组类型)特定的延迟。

注意:如果外部控制器要求 PHY 运行在环回模式(LBMODE 设置),那么 WL 的值应减去 1。

RL(读延迟):

- DDR4:RL = (CAS 延迟(CL) + 加法延迟(AL) + CA 奇偶校验延迟(PL) + RDIMM/LRDIMM 可编程命令延迟加法器)。

- DDR3:RL = (CAS 延迟 + 加法延迟)。

- LPDDR2/LPDDR3:RL = (SDRAM 读取延迟 + DTPR3.TDQSCK)。

RL 是从控制器发出读命令到数据被读取并准备好给系统使用的时间延迟。在不同的内存类型中,计算公式也有所不同,尤其是对于 LPDDR2/LPDDR3,还需要额外考虑 DTPR3.TDQSCK 这一寄存器字段(具体的配置项可以参考寄存器描述)。

2. PUAD 和 ZUEN

PUAD(即 DSGCR.PUAD)是一个寄存器字段的值,其与控制器在 HDR 模式和 CSDR 模式下的配置相关。如果 PUAD 值不是 4,则需要根据以下公式进行调整:

- HDR 模式:调整值为 **2 * (PUAD – 4)**。

- CSDR 模式:调整值为 **(PUAD – 4)**。

这意味着,在不同的操作模式下,PUAD 的调整会影响时序的准确性,需要根据具体模式来调整延迟。

ZUEN(即 DSGCR.CTLZUEN 和 DSGCR.PHYZUEN)是另一个寄存器字段,它的值与控制器配置相关,影响 PUAD 的设置。

3. DQS Drift Detection 和 Compensation

如果启用了 DQS 漂移检测与补偿,并且配置为在控制器更新时进行更新,那么这个参数的值可能会比正常情况下更高,具体取决于控制器如何配置虚拟读取(dummy reads)以进行漂移补偿。这种补偿机制是为了减少 DQS(数据选通信号)因时钟漂移而导致的时序误差。

7.4.1.1 读延迟的详细说明

表 7-2 描述了 DFI 命令 到 DFI 读数据有效信号(dfi_valid) 的 读延迟。这个过程涉及 PUB 和 PHY 模块。描述中提到的延迟适用于 上升到上升模式(rise-to-rise mode),即从时钟信号的一个上升沿到下一个上升沿的时间延迟。

- 如果使用 上升到下降模式(rise-to-fall mode),则命令延迟和读数据延迟分别减少 1 个 tCK(SDRAM 时钟周期)。因此,整体的读延迟减少了 2 个 tCK。这意味着在上升到下降模式下,PHY 和 DFI 接口之间的时序要求会变得更加严格,数据的传输和处理速度会有所提升。

本文链接: https://talent-tudou.github.io/2024/12/20/DDR/PUB-Timing/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!