uMCTL2手册2.25.1,SDRAM低功耗

2.25.2 SDRAM Power Saving Features

1. 多rank系统中的省电模式

- 在 多rank(多通道)系统 中,省电模式不能按每个rank(内存通道)单独应用,而是全局应用的。

- 应用全局模式 意味着无论内存系统有多少个rank,当启用省电模式时,这些模式会对所有rank生效。

2. 自动进入和退出预充电省电模式(Precharge Power-Down Mode)

- 预充电省电模式 是一种控制内存消耗的省电模式。当启用时,uMCTL2(内存控制器)会根据可编程的空闲超时自动进入或退出该模式。

- 这意味着,当内存没有发生读写操作时,控制器会在空闲一定时间后进入预充电省电模式,降低功耗。

3. 自刷新模式(Self-Refresh)

- 自刷新模式是一种低功耗模式,内存控制器会在没有外部时钟输入的情况下进行自我刷新,以保持数据的完整性。自刷新模式有三种控制方式:

- 通过可编程的空闲超时周期,类似于预充电省电模式的空闲超时。

- 通过软件显式控制,即系统软件可以直接控制何时进入或退出自刷新模式。

- 通过硬件低功耗接口,硬件可以自动进入自刷新模式。

4. 深度电源关断(Deep Power-Down,DPD)和最大功耗节省模式(Maximum Power Saving Mode,MPSM)

- 深度电源关断(DPD) 和 最大功耗节省模式(MPSM) 是两种更强的省电模式,它们通过减少内存和控制器之间的活动来最大限度降低功耗。

- 控制方式:可以通过软件显式控制何时进入或退出这两种模式。

5. DFI时钟禁用(dfi_dram_clk_disable)

dfi_dram_clk_disable

是一个信号,可以用来禁用内存的时钟。内存控制器可以在以下模式下禁用时钟:

- 自刷新模式(Self-refresh),但对于LPDDR4除外。

- 自刷新电源关断模式(Self-refresh power down),只适用于LPDDR4。

- 电源关断模式(Power-down)。

- 深度电源关断模式(Deep power-down)。

- 最大功耗节省模式(Maximum power saving mode)。

- 时钟停止(Clock stop),如果使用的是mDDR、LPDDR2、LPDDR3、LPDDR4内存。

6. 硬件低功耗接口(Hardware Low Power Interface)

- 在硬件低功耗接口支持下,cactive_ddrc信号可以在空闲条件下被拉低,这会发生在以下几种模式下:

- 正常模式(normal mode)。

- 电源关断模式(power-down mode)。

- 自动自刷新模式(automatic self-refresh mode)。

- 另外,如果需要强制退出这些低功耗模式,可以通过设置 cactive_in_ddrc = 1 来实现。

7. 注意事项

- 避免同时启用深度电源关断和最大功耗节省模式:

- 不建议同时启用 深度电源关断模式(DPD) 和 最大功耗节省模式(MPSM),因为这可能导致系统的不稳定或无法预期的行为。

- 可以同时启用电源关断模式和自刷新模式:

- 电源关断模式(Power-down)和自刷新模式(Self-refresh)可以同时启用。可以通过设置以下寄存器实现:

- PWRCTL.powerdown_en = 1:启用电源关断模式。

- PWRCTL.selfref_en = 1:启用自动自刷新模式。

- PWRCTL.selfref_sw = 1:启用软件控制的自刷新模式。

- 电源关断模式(Power-down)和自刷新模式(Self-refresh)可以同时启用。可以通过设置以下寄存器实现:

- dfi_dram_clk_disable的有效组合:

- 启用 dfi_dram_clk_disable 是与上述省电模式(包括自刷新模式、电源关断模式等)兼容的。

8. 空闲计时器(Idle Timer)

- 在 PWRTMG/HWLPCTL 寄存器中有一些字段用来连续倒计时,以确定控制器的空闲状态。这些计时器字段会根据以下情况倒计时:

- 控制器进入空闲状态时,开始计时。

- 这些计时器会倒计时,不受 PWRCTL 或 HWLPCTL 寄存器使能位的影响。

- 计时器的工作条件:

- HIF命令没有发生。

- 维护或周期性命令没有发生,如刷新(Refresh)、ZQ、MR4命令等。

- 软件驱动的命令(如刷新、MRR/MRW、ZQ等)没有发生。

2.25.2.1 Precharge Power-down

1. 进入预充电省电模式的条件和步骤

首先,预充电省电模式 是一种低功耗状态,目的是在内存系统空闲时降低功耗。uMCTL2(内存控制器)会根据设置的条件自动进入此模式。

启用预充电省电模式

- 当寄存器 PWRCTL.powerdown_en = 1 时,表示允许控制器进入省电模式。

- 控制器会在空闲时间(即没有维护命令或软件命令,如刷新、MR、ZQ等)持续达到 PWRTMG.powerdown_to_x32 设置的空闲时长后,进入预充电省电模式。

2. 预充电省电模式的进入步骤

进入预充电省电模式涉及以下几个步骤:

步骤1:刷新命令

- 如果之前退出了自刷新模式,则必须至少发出一次刷新命令(或者如果启用了 LPDDR2/3/4 的每bank刷新模式,则为每个bank发出8次刷新命令),以确保所有活跃的rank得到刷新。

- 自动刷新逻辑 必须启用,或者可以通过 DBGCMD.rank*_refresh 命令显式地触发刷新。

- 注意:如果没有刷新命令或命令没有正确发出,预充电省电模式的进入可能会失败。

步骤2:关闭所有打开的行(Precharging)

- 关闭所有打开的页面(即关闭内存中的行)。内存行是逐个关闭的,顺序没有明确要求。

- 预充电(precharge) 是指将内存的活跃行关闭,使得内存进入准备状态,可以进入省电模式。

- 此步骤确保内存不再有打开的行,从而减少功耗。

步骤3:等待 tRP 闲置周期

- 等待 tRP(行预充电)闲置周期。tRP 是内存中用于关闭一个行并准备下一个行的时间。这个步骤是确保所有的行都已关闭并准备好进入省电模式。

步骤4:发出预充电省电模式进入命令

- 发出 预充电省电模式进入命令,通常是 NOP/deselect 命令,并且 CKE信号被设置为0(表示时钟使能被禁用,进一步降低功耗)。

- 多rank系统:如果系统中有多个rank,所有rank的芯片选择(chip-select)信号必须同时被拉高,确保所有rank同时进入预充电省电模式。

- 如果启用了 DIMMCTL.dimm_stagger_cs_en 并且 MSTR.ddr4 == 0,则预充电命令会分别针对偶数和奇数rank发出。

步骤5:如果启用了DFI低功耗接口

- 如果启用了 DFI低功耗接口(DFILPCFG0.dfi_lp_en_pd),则会尝试通过该接口进入低功耗模式,且 dfi_lp_wakeup会被设置为

DFILPCFG0.dfi_lp_wakeup_pd- 低功耗模式的进入会有一个延迟,由 DFITMG0.dfi_t_ctrl_delay + DRAMTMG7.t_ckpde 计算得出的时钟周期组成。

- 该延迟是为了满足SDRAM时序要求,因为在PHY被配置为关闭时钟以节省最大功耗时,需要等待足够的时间。

3. 中途被打断的情况

- 如果在 步骤2 或 步骤3 期间接收到来自SoC的读/写请求,预充电省电模式的进入会被立即中止。

- 同样,如果在这两个步骤中,寄存器 PWRCTL.powerdown_en 被设置为0,则预充电省电模式的进入也会被中止。

4. 发出进入命令后需要正确退出

- 一旦发出了预充电省电模式进入命令,接下来必须按照 “退出预充电省电模式” 中的描述,正确退出该模式。

2.25.2.1.2 Exiting Precharge Power-down

1. 触发预充电省电模式退出的条件

当 uMCTL2 将 DDR SDRAM 设备置于预充电省电模式后,以下几种情况会导致 uMCTL2 自动退出该模式:

- 需要刷新操作:如果系统中某个rank需要刷新,uMCTL2会退出预充电省电模式。

- 接收到来自SoC的新请求:如果SoC发出新的读写请求,uMCTL2会退出预充电省电模式。

- 请求进入自刷新模式:如果需要进入自刷新模式,uMCTL2会退出预充电省电模式。

- PWRCTL.powerdown_en 被设置为 0:如果控制器的电源管理使能寄存器的

powerdown_en位被设置为 0,uMCTL2会退出预充电省电模式。

2. 退出预充电省电模式的步骤

当触发上述条件时,uMCTL2 会按照以下步骤退出预充电省电模式:

步骤 1:发出 NOP/deselect 命令

- 为了满足 tCKE的时序要求(时钟使能的要求),在退出预充电省电模式之前,uMCTL2 需要发出 NOP/deselect命令。

- NOP(No Operation)命令用于保持总线空闲。

- deselect 命令表示不选择任何芯片,使得时钟信号和控制信号在此时不被禁用。

步骤 2:如果使用了 DFI 低功耗模式,则退出低功耗模式

- 如果在进入预充电省电模式时,使用了 DFI低功耗模式,uMCTL2 会在退出时也退出该低功耗模式。

- 退出 DFI 低功耗模式的时间会受到

DFILPCFG0.dfi_lp_wakeup_pd的影响,该时间被称为 wake-up time。- 退出时的最小时间间隔为 DFITMG1.dfi_t_dram_clk_enable + DRAMTMG6.t_ckpdx 时钟周期。这个时序保证了在进入正常工作状态之前,PHY时钟和信号恢复的足够时间。

步骤 3:发出电源退出命令

- 发出 电源退出命令,通常是 NOP/deselect 命令,并将 CKE信号设置为1,这表示时钟使能已经恢复,允许内存继续工作。

- 对于多rank系统,所有的 芯片选择(chip-select)信号需要同时拉高,确保所有rank同时退出预充电省电模式。

步骤 4:发出 NOP/deselect 命令以满足 tXP 时序

- 在退出预充电省电模式后,uMCTL2 会发出 NOP/deselect 命令,持续一段时间,这个时间由 tXP 参数定义。tXP 是一个预定义的时序参数,确保内存在退出省电模式后保持稳定。

3. 不同DDR协议对预充电省电模式退出的要求

在不同的 DDR协议 中,预充电省电模式的退出有一些不同的要求,具体包括:

DDR2:快速退出与慢速退出

- DDR2 标准中描述了两种不同的 活动省电模式 退出方式,这取决于 MR bit 12 的配置。但是,uMCTL2 使用的是 预充电省电模式,而不是活动省电模式,因此此配置对 uMCTL2 和 SDRAM设备 没有影响。

DDR3:快速退出与慢速退出

- DDR3标准也有两种不同的 预充电省电模式退出方式,取决于 MR0 bit 12的配置:

- 慢速预充电省电模式:如果 MR0[12] = 0,则 DRAMTMG1.t_xp 必须设置为 tXPDLL。

- 快速预充电省电模式:如果 MR0[12] = 1,则 DRAMTMG1.t_xp 必须设置为 tXP。

其他DDR协议

- 对于 其他支持的DDR协议,没有规定快速与慢速退出模式的区别。

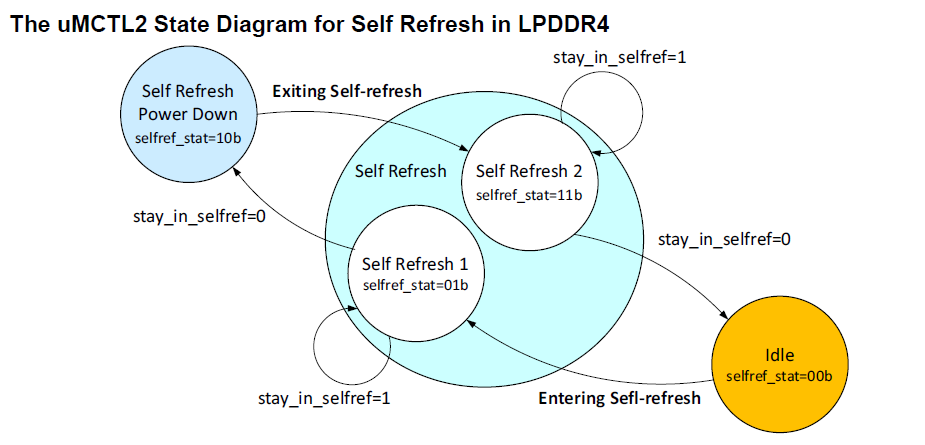

2.25.2.2 Self-refresh

1. LPDDR4的自刷新模式(Self-refresh)

在 LPDDR4 中,自刷新模式和自刷新省电模式是两种不同的低功耗模式。每种模式的工作方式如下:

自刷新模式(Self Refresh)

在 自刷新模式 下,外部时钟输入仍然是必需的。虽然所有输入引脚都保持活跃状态,但是 SDRAM 只会接受特定的命令,不会接受其它命令。

自刷新模式下,SDRAM 仍然能处理一些命令,但不包括 PASR Bank/Segment 设置

。允许的命令包括:

- MRR-1(内存读命令)

- CAS-2(CAS 延迟命令)

- SRX(自刷新退出命令)

- MPC(模式寄存器编程命令)

- MRW-1 和 MRW-2(模式寄存器写入命令)

自刷新省电模式(Self Refresh Power Down)

- 这是 LPDDR4 的一种进一步降低功耗的模式。具体细节没有在这段描述中展开,但通常,它会比普通的自刷新模式消耗更少的功率。

2. uMCTL2控制器的状态和行为

- STAT.selfref_state 寄存器是 uMCTL2 控制器用来跟踪自刷新状态的寄存器。它指示控制器是否处于自刷新模式或自刷新省电模式。

自刷新状态的转换

- STAT.selfref_state 寄存器有两个比特位,用于表示当前的状态。这些状态值的解释如下:

- 2’b01:表示控制器进入了 自刷新模式。

- 2’b10:表示从 自刷新模式 转换到 自刷新省电模式。

- 2’b11:表示进入 自刷新省电模式,之后会进入 退出状态(例如,恢复到正常模式)。

- 2’b00:表示控制器退出了自刷新模式或自刷新省电模式,恢复正常工作。

- 状态转换要求如下:

- 从 2’b01(自刷新模式)转换时,必须进入 2’b10(自刷新省电模式)。

- 从 2’b11(自刷新省电模式)转换时,必须进入 2’b00(退出状态)。

3. uMCTL2 控制器的其他寄存器

- PWRCTL.stay_in_selfref 寄存器:这个寄存器用于控制是否保持在自刷新模式中。如果启用了该寄存器,则即使外部发生某些事件,uMCTL2 也会继续保持在自刷新模式中。

- 在自刷新模式下,uMCTL2 可以继续执行以下命令:

- MRR(内存读命令)

- MRW(内存写命令)

- SRX(自刷新退出命令)

这些命令允许 uMCTL2 在自刷新模式下进行一些必要的操作,比如读取或写入模式寄存器,或者退出自刷新模式。

Entering Self Refresh

触发自刷新模式的条件

1. 自动自刷新(Automatic Self Refresh)

- 当 PWRCTL.selfref_en 位被设置时(即启用自刷新模式),并且在指定的时间内(由 PWRTMG.selfref_to_x32 指定),uMCTL2 内没有待处理的读写操作,控制器会自动进入自刷新模式。

2. PHY 主接口触发

- 当 PHY Master Interface 启用(设置 DFIPHYMSTR.dfi_phymstr_en 位),并且从 PHY 设备发出 dfi_phymstr_req 请求时,uMCTL2 也会进入自刷新模式。在此期间,控制器 不会 执行当前排队的命令,直到进入自刷新模式。

3. 软件触发的自刷新(Software-triggered Self-refresh)

- 当 PWRCTL.selfref_sw 位被设置时,控制器会进入软件触发的自刷新模式。在此情况下,用户可以选择是否在进入自刷新模式之前执行当前排队的命令。如果选择不执行这些命令,控制器会更快地进入自刷新模式,避免排空缓存队列(CAMs)。

- 具体操作:

- 如果 PWRCTL.dis_cam_drain_selfref 设置为 0,控制器会阻止接收新的命令,并执行当前的命令,直到进入自刷新模式。

- 如果 PWRCTL.dis_cam_drain_selfref 设置为 1,控制器会仅在没有待执行的命令时才阻止新的命令,不会执行已排队的命令。

4. 硬件触发的低功耗自刷新(Hardware Low Power Self-refresh)

- 当硬件请求低功耗自刷新(例如通过 csysreq_ddrc/csysack_ddrc 信号)且满足以下条件时,uMCTL2 会进入自刷新模式:

- 当前没有待执行的命令。

- 控制器没有处于初始化、深度关机或最大功耗节省模式。

- 这会导致 hif_cmd_stall 信号被驱动为高电平,阻止接收新的命令,并且现有的命令会执行,直到进入自刷新模式。

5. DDR4 CA 校验和(Parity)

- 如果启用了 DDR4 校验和(CA parity)并且 CRCPARCTL1.caparity_disable_before_sr 设置为 1,uMCTL2 在进入自刷新模式之前会禁用 CA 校验和,并在退出自刷新模式后重新启用 CA 校验和。

6. DDR4 CAL 模式

- 如果启用了 DDR4 CAL(Calibration),uMCTL2 会在进入自刷新模式之前禁用 CAL 模式,并在退出自刷新模式后重新启用它。

进入自刷新模式的步骤

- 等待刷新命令

- 如果之前曾处于自刷新退出状态,uMCTL2 必须先发出至少一个刷新命令(对于每个活动的 rank)。如果启用了自动刷新逻辑或通过软件直接发出刷新命令,就会进入下一个步骤。

- 如果某些 rank 被禁用刷新(通过 **RFSHCTL3.rank_dis_refresh[N]**),那么这些 rank 不会收到刷新命令。

- 关闭所有打开的页面

- uMCTL2 会关闭所有已打开的页面。关闭的顺序不固定,可以逐个关闭。

- 等待tRP闲置周期

- 这一步是等待 tRP(行预充电)时间间隔,以确保在进入自刷新模式之前不会有任何新的命令到达。如果在此期间有新的命令到达控制器,进入自刷新模式的过程将被中断。

- 发出自刷新命令

- 发出进入自刷新模式的命令,这通常是通过将 RAS 和 CAS 信号置为高,同时将 CKE 置为低来实现。

- 如果是多 rank 系统,所有的 chip-select 都会被同时激活,确保所有 rank 同时进入自刷新模式。

- 如果启用了 DIMMCTL.dimm_stagger_cs_en,且 MSTR.ddr4 == 0,自刷新命令会分别为偶数和奇数 rank 发出。

- DFI 低功耗接口(可选)

- 如果启用了 DFI 低功耗接口(通过 DFILPCFG0.dfi_lp_en_sr),在进入自刷新模式时,uMCTL2 会尝试通过 DFI 低功耗接口进入低功耗模式。此时,会等待一定的时间(由 DFITMG0.dfi_t_ctrl_delay 和 DRAMTMG5.t_cksre 定义),以确保 PHY 在关闭时钟时不会违反时序要求。

- 如果是由 PHY 主接口 触发的自刷新模式,这一步会被跳过,因为在 PHY 请求期间 DFI 低功耗接口已被禁用。

状态优先级和退出条件

- 自动自刷新(由 PWRCTL.selfref_en 触发)优先级最低,软件自刷新和硬件低功耗自刷新具有较高优先级,而由 PHY 主接口触发的自刷新具有最高优先级。

- 当 PHY 主接口请求 时,自刷新退出只能在 PHY 主接口请求被解除后发生。

- 如果是 软件自刷新 触发的自刷新模式,则只有在软件自刷新退出时,才会退出自刷新模式。

- 如果是 硬件低功耗自刷新 触发的自刷新模式,则只有在硬件低功耗自刷新退出时,才会退出自刷新模式。

Exiting Self-refresh

1. 退出自刷新模式的触发条件

uMCTL2 会在以下情况下将 DDR SDRAM 设备从自刷新模式中移出:

- PWRCTL.selfref_en 输入去反(de-asserted):也就是 PWRCTL 寄存器中的

selfref_en位被置为 0,或者当接收到新的命令时,如果自刷新是唯一触发自刷新模式的原因。 - PHY 主接口启用:如果 PHY 的主接口(DFI PHY Master Interface)被启用(即设置

dfi_phymstr_en),并且 PHY 发出了dfi_phymstr_req(请求),那么自刷新会被终止。 - 软件自刷新退出:如果

PWRCTL.selfref_sw位被去反,表示软件请求退出自刷新模式,这被称为软件自刷新退出。 - 硬件低功耗退出请求:当有硬件低功耗退出请求(例如在

csysreq_ddrc/csysack_ddrc信号上)时,也会退出自刷新模式。

2. 退出自刷新模式的步骤

退出自刷新模式涉及多个步骤,确保 DDR 控制器能够恢复正常的操作。

- 插入必要的 NOP(无操作)/deselect(取消选择)命令: 这些命令是为了满足进入自刷新模式时的时序要求,比如

tCKE(时钟使能延迟),tCKESR(时钟使能恢复),tSR(自刷新延迟)等。 - 按照 DFI 规范发出控制更新请求: 如果

DFIUPD0.dis_auto_ctrlupd_srx = 0且DFIUPD0.ctrlupd_pre_srx = 1,则需要按照 DFI(DDR 总线接口)规范发出dfi_ctrlupd_req(控制更新请求)。- 对于 LPDDR4,如果没有进入电源管理模式(Power Down),则不需要发出该请求。只有在 PHY 主接口请求时才会触发。

- 如果进入自刷新时使用了 DFI 低功耗模式,则退出低功耗模式: 如果使用了 DFI 低功耗接口(通过

DFILPCFG0.dfi_lp_en_sr),退出自刷新模式时,低功耗模式会在指定的时间后退出,但必须等待DFITMG1.dfi_t_dram_clk_enable + DRAMTMG5.t_cksrx时钟周期。 - 发出退出自刷新命令: 一旦满足时序要求,控制器将发出“退出自刷新”命令,这通常通过断开

RAS和CAS信号并将CKE(时钟使能)设置为 1 来实现。- 对于 LPDDR4,如果

PWRCTL.stay_in_selfref被设置为 1,uMCTL2 在发出退出命令之前不会退出自刷新模式。只有在去除该位之后,才会进入空闲状态(Idle state)。 - 如果 PHY 主接口在发出退出命令前发出了

dfi_phymstr_req,则自刷新模式不会退出,直到该请求被去反(de-asserted)。

- 对于 LPDDR4,如果

- 发出控制更新请求(如有需要): 如果

DFIUPD0.dis_auto_ctrlupd_srx = 0且DFIUPD0.ctrlupd_pre_srx = 0,则继续按照 DFI 规范发出dfi_ctrlupd_req请求。- 同样,对于 LPDDR4,如果没有进入电源管理模式,则不会发出该请求,只有在 PHY 主接口请求时才会触发。

- 发出 NOP/deselect 命令: 为了满足时序要求,发出 NOP 或 deselect 命令,直到指定的

tXSDLL、tXSNR和tXSRD时序(这些时序值是自刷新退出命令和后续操作之间的时间间隔)。

3. 自刷新退出时的时序控制

DRAMTMG8 和 DRAMTMG14 寄存器:这些寄存器包含了自刷新退出时的时序控制字段。不同的 DDR 类型有不同的时序要求:

- DDR2/3/4:使用

t_xs_dll_x32(对于需要锁定 DLL 的命令,如读命令、写命令、MPR 命令等)或者t_xs_x32(对于不需要锁定 DLL 的命令)。 - DDR4:支持快速自刷新退出模式,用于 ZQCL 和 ZQCS 命令,时序由

t_xs_fast_x32控制。 - 自刷新中止模式:针对 DDR4,还支持自刷新中止模式,这个模式是由

MR4寄存器中的 A9 位控制的,时序由t_xs_abort_x32控制。

- DDR2/3/4:使用

注意事项:

PWRCTL.stay_in_selfref = 1:这个设置会使 DDR 控制器保持在自刷新模式下,不会退出,通常是为了执行 MRR/MRW 命令。- 通常情况下不应该设置为 1,除非 SoC 确实需要在自刷新模式下执行这些特殊的操作(MRR/MRW)。否则,系统会停滞在自刷新模式,无法继续其他操作。

2.25.2.3 Deep Power-down

2.25.2.3.1 Entering Deep Power-down

1. 进入 Deep Power-down 模式的条件

要将内存设备进入 Deep Power-down 模式,必须满足以下几个条件:

- PWRTMG.powerdown_to_x32 已经过期且 uMCTL2 处于空闲状态(除非发出刷新命令):

PWRTMG.powerdown_to_x32是一个定时器,定义了进入深度节能模式的最短等待时间。只有在这个时间已经过去并且 uMCTL2 控制器空闲时,才能进入 Deep Power-down。

PWRCTL.selfref_sw = 0:- 这意味着自刷新模式(Self Refresh)没有被软件触发,即不处于自刷新状态。

PWRCTL.selfref_en = 0:- 这表示没有开启硬件自刷新模式(Self Refresh Enable)。

- 硬件低功耗接口条件(

HWLPCTL.hw_lp_en = 1):- 如果硬件低功耗接口(HWLPCTL)被启用,Deep Power-down 模式只有在自刷新退出后才能进入。这可以通过检查

STAT.operating_mode和STAT.selfref_type来确认。

- 如果硬件低功耗接口(HWLPCTL)被启用,Deep Power-down 模式只有在自刷新退出后才能进入。这可以通过检查

HWLPCTL.hw_lp_exit_idle_en = 1:- 如果这个条件被启用,只有在系统空闲并且

cactive_in_ddrc寄存器的所有位为零时,才能进入 Deep Power-down 模式。cactive_in_ddrc表示 DDR 控制器当前活动的状态。

- 如果这个条件被启用,只有在系统空闲并且

2. 进入 Deep Power-down 模式的步骤

进入 Deep Power-down 模式时,DDR 控制器必须按照以下步骤操作:

1. 等待自刷新退出:

- 如果之前有自刷新退出命令,必须等待至少一个刷新命令(对于 LPDDR2/LPDDR3/4,可能是每个银行 8 个刷新命令)到达所有活动的行。这个刷新命令必须是自动刷新,或者通过软件直接发起的刷新命令。

2. 预充电所有打开的页:

- 必须关闭所有打开的页面(行),每个页面一次关闭。关闭页面的顺序没有特别要求。

3. 等待 tRP(行预充电)空闲时间:

- 在进入 Deep Power-down 之前,必须等待行预充电时间(tRP)。这段时间用来确保所有操作都能正常完成。

4. 发出进入 Deep Power-down 的命令:

- 在多通道系统中,必须同时对所有通道发出 Deep Power-down 命令,确保所有通道都进入 Deep Power-down 模式。

- 对于不同类型的 DDR,发出的命令格式有所不同:

- mDDR:

CKE = 0, CSN = 0, RAS = 1, CAS = 1, WE = 0 - LPDDR2/LPDDR3:

CKE = 0, CSN = 0, CA0 = 1, CA1 = 1, CA2 = 0

- mDDR:

5. 低功耗接口设置:

- 如果启用了低功耗接口(

DFILPCFG0.dfi_lp_en_dpd),此时会尝试通过 DFI(DRAM 控制接口)低功耗接口进入低功耗模式。设置dfi_lp_wakeup_dpd可以指定唤醒时间,确保符合 SDRAM 时序要求。 - 在发出低功耗模式命令之前,会有一定的延时,这个延时由

DFITMG0.dfi_t_ctrl_delay和DRAMTMG6.t_ckdpde这两个寄存器控制,主要是为了满足 PHY 时钟关闭后的时序要求。

3. 中断 Deep Power-down 模式的条件

如果在步骤 1 或步骤 3 期间,系统收到读取或写入请求,或者在步骤 1 或步骤 3 期间将 PWRCTL.deep_powerdown_en 设置为 0,那么 Deep Power-down 进入命令会被立即中断。

4. 注意事项

- 进入深度掉电模式时,SDRAM 的内容可能会丢失。

2.25.2.3.2 Exiting Deep Power-down

退出 Deep Power-down 模式的条件

当 uMCTL2(内存控制器)将 DDR SDRAM 设备置于 Deep Power-down 模式时,它将在以下情况发生时自动退出该模式并重新运行初始化序列:

- PWRCTL.deeppowerdown_en 设置为 0 时,控制器会自动退出 Deep Power-down 模式。

- 如果在进入 Deep Power-down 时启用了 DFI 低功耗模式,那么在退出 Deep Power-down 前,必须先退出 DFI 低功耗模式。

退出 DFI 低功耗模式需要等待一定的唤醒时间,这个时间由 DFILPCFG0.dfi_lp_wakeup_dpd 寄存器指定,并且不能早于 DFITMG1.dfi_t_dram_clk_enable + DRAMTMG6.t_ckdpdx 时钟周期。

退出 Deep Power-down 模式的步骤

1. 防止 uMCTL2 提前激活 DFI(dfi_cke)信号

在退出 Deep Power-down 时,必须确保 SDRAM 初始化 完成后才激活 DFI 信号,以免在初始化完成前尝试恢复操作。因此,在清除 PWRCTL.deeppowerdown_en 前,必须将 INIT0.skip_dram_init 设置为 2'b11。

INIT0.skip_dram_init = 2'b11表示跳过对 SDRAM 初始化的设置(这一步用于等待初始化完成)。

2. 禁用自动控制更新和软件控制器更新

为了防止在 INIT0.skip_dram_init 值从 2'b11 改为 2'b01(即开始初始化)时发生控制更新,必须禁用一些自动控制更新和软件控制器更新。具体步骤如下:

- 禁用自动控制更新:通过设置

DFIUPD0.dis_auto_ctrlupd来禁用自动控制更新。 - 禁用高效接口(HIF):通过设置

DBG1.dis_hif禁用高效接口。 - 停止发送软件控制更新:确保在退出 Deep Power-down 模式前不再发送任何软件控制更新。

这些步骤确保在状态改变期间,控制器不会触发不必要的更新。

3. 清除 DFIMISC.dfi_init_complete_en

在清除 PWRCTL.deeppowerdown_en 前,还需要确保清除 DFIMISC.dfi_init_complete_en 寄存器为 0,以确保 uMCTL2 在 PHY 完成初始化之前不会继续进行下一步操作。

4. 清除 PWRCTL.deeppowerdown_en 并启动 SDRAM 初始化

- 将

PWRCTL.deeppowerdown_en清除为0后,可以通过轮询STAT.operating_mode来检测 uMCTL2 是否退出了 Deep Power-down 模式。 - 一旦 uMCTL2 退出 Deep Power-down,便可以通过设置

PUB_PIR寄存器来启动 SDRAM 初始化。

5. 恢复 skip_dram_init 的旧值

如果在步骤 1 中已经修改了 skip_dram_init 的值(例如从 2'b01 改为 2'b11),那么在启动初始化后,需要将 skip_dram_init 恢复为其旧的值。

6. 轮询 PGSR 寄存器,检测 PHY 初始化是否完成

- 在设置

PUB_PIR寄存器后,需要通过轮询 PUB 的 PGSR(PHY 状态寄存器)来检测 PHY 初始化是否完成。

7. 恢复控制更新并重新启动软件更新

- 在步骤 2 中禁用的自动控制更新和软件控制器更新,在此步骤中需要恢复。

- 如果之前禁用了这些更新(

DFIUPD0.dis_auto_ctrlupd和DBG1.dis_hif),需要将它们恢复为原来的值,或者重新开始发送软件控制器更新。

8. 设置 DFIMISC.dfi_init_complete_en 为 1

最后,设置 DFIMISC.dfi_init_complete_en 为 1,以允许 uMCTL2 的状态机退出初始化状态,完成 Deep Power-down 模式的退出。

后面待定

本文链接: https://talent-tudou.github.io/2024/12/14/DDR/uMCTL2-SDRAM Power Saving Features/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!