2.7.1 DFI更新概述

DFI(内存控制器接口)更新接口用于传输内部设置的更新,这些更新是为了补偿环境条件的变化,主要是处理PVT(工艺/电压/温度)变化对延迟线等设置的影响。这个接口涉及信号和时序参数,确保在更新过程中不会干扰到DRAM接口的信号传输。为了避免更新时对信号产生干扰,DFI支持更新模式,在这些模式下,DFI总线必须处于空闲状态,即不进行任何数据传输。

2.7.2 DFI控制器发起的更新请求

DFI控制器发起的更新请求(dfi_ctrlupd_req)是由uMCTL2(内存控制器)在DFI接口上发出的信号,目的是让PHY(物理层)更新延迟线的值。延迟线用于调整信号的时序,确保数据在正确的时间被读取或写入。

- dfi_ctrlupd_req:这是一个请求信号,发出后会触发PHY更新延迟线。为了应对环境变化(如温度变化、电压波动等),控制器需要定期发出这个信号,确保延迟线能够适应这些变化。

- phy_dfi_ctrlupd_ack:这是一个确认信号,表示PHY完成了延迟线更新的操作。只有在收到这个确认信号后,控制器才知道延迟线更新已经完成。

延迟线更新必须小心处理,不能在读或写操作期间进行,因为这样可能会破坏数据眼(数据有效区域的稳定性)。因此,在进行延迟线更新时,必须确保读写操作不会受到影响。

如果PHY正在进行更新(即dfi_phyupd_ack = 1),uMCTL2会延迟发出dfi_ctrlupd_req请求,以避免冲突。

两种DFI更新方法

- 自动MC发起的更新请求(Automatic MC-Initiated Update Request):这意味着内存控制器自动定期发起更新请求,而不需要外部干预。

- MC发起的更新请求的直接软件请求(Direct Software Request of MC-initiated Update Request):在这种方法下,软件(如操作系统或固件)直接发起更新请求,控制更新过程。

2.7.2.1 自动MC发起的更新请求

- DFIUPD0.dis_auto_ctrlupd = 0:如果这个配置项被设置为0,那么就启用自动MC发起的更新请求。这意味着内存控制器(uMCTL2)会在特定时机自动发起更新请求,而不需要外部软件的干预。

- uMCTL2控制dfi_ctrlupd_req信号:uMCTL2必须小心地控制

dfi_ctrlupd_req信号的触发。这个信号的作用是请求PHY(物理层)进行延迟线更新。uMCTL2会在空闲状态时发出dfi_ctrlupd_req信号。空闲状态被定义为:- 没有读取或写入操作正在进行(即在CAMs中没有读取或写入周期);

- 没有读取响应在RT(响应追踪器)块中缓存;

- 没有写入数据在MR(内存读取)块中等待。

- 强制DFI更新请求:如果uMCTL2长时间没有进入空闲状态(即没有空闲的时刻发出更新请求),则它会使用超时机制。当发生DFI MC发起更新超时时,uMCTL2会暂停读写操作,直到MR和RT块都进入空闲状态,此时才会发出

dfi_ctrlupd_req信号。

特定配置下的行为

对于单排配置(即只有一个内存rank)且只有读写流量的情况,特别是:

DFIUPD1.dfi_t_ctrlupd_interval_max_x1024 = 255DFIUPD0.dis_auto_ctrlupd_srx = 1- 禁用每bank的刷新操作(

RFSHCTL0.per_bank_refresh = 0)

这种配置下,uMCTL2只有在刷新命令之后才会发送

dfi_ctrlupd_req信号。触发频率设置:

DFIUPD1.dfi_t_ctrlupd_interval_min_x1024字段设置了dfi_ctrlupd_req信号的触发频率。如果这个值设置得较小,那么dfi_ctrlupd_req会在每次刷新命令后触发;如果设置得较大,则dfi_ctrlupd_req会在每n次刷新命令后触发。自刷新退出命令:如果

DFIUPD0.dis_auto_ctrlupd_srx = 0,则dfi_ctrlupd_req信号会在每次自刷新退出命令之前或之后触发,具体取决于DFIUPD0.ctrlupd_pre_srx的设置。

注意事项

- 如果启用了每bank的刷新功能,或者

DFIUPD1.dfi_t_ctrlupd_interval_min_x1024设置得较高,并且使用了刷新突发(refresh bursts),那么dfi_ctrlupd_req信号可能会在刷新命令以外的命令后被触发。

2.7.2.2 直接软件请求MC发起的更新请求

- DFIUPD0.dis_auto_ctrlupd = 1:当这个配置项被设置为1时,意味着禁用了自动控制更新请求,转而由SoC来决定何时发起更新请求。这样做的目的是在某些特殊场景下,比如内存带宽利用率至关重要的情况下,避免更新请求打断正常的读写事务。

- SoC控制更新请求:在这种模式下,SoC可以决定何时执行DFI MC发起的更新请求。这对于那些对内存带宽要求非常严格的应用尤为重要,特别是当uMCTL2希望保持连续的内存操作,而不希望任何中断时。

执行更新请求的方式

- 设置DBGCMD.ctrlupd = 1:为了发起更新请求,SoC需要通过设置DBGCMD.ctrlupd寄存器位为1,告知uMCTL2发起DFI更新请求。这个请求会被存储在uMCTL2中,一旦请求被接受,DBGCMD.ctrlupd寄存器位会被自动清除。

- 条件:DBGSTAT.ctrlupd_busy:SoC只有在DBGSTAT.ctrlupd_busy信号为低电平(low)时,才可以执行更新请求。这个信号表示uMCTL2是否正在忙于处理更新请求。当uMCTL2接受到请求后,

ctrlupd_busy会变为高电平(high),表示uMCTL2正在处理这个请求。处理完成后,信号会恢复为低电平,表示可以接受新的更新请求。

DFI更新与刷新操作的协调

- 同时发起DFI更新和刷新:uMCTL2可以在刷新命令和DFI更新请求同时进行时发起

dfi_ctrlupd_req信号。对于刷新操作和DFI更新请求,uMCTL2会确保这两者按正确的顺序发生,不会发生功能上的冲突。 - 时机的选择:SoC需要在控制器能够容忍读写调度中断的时刻发起DFI更新请求。虽然SoC有控制的权限,但更新请求仍然会受到uMCTL2的调度约束,以确保不影响系统的正常操作。SoC的逻辑需要确保更新请求被合理频繁地调度,并且在合适的时机发起。

2.7.3 DFI PHY-initiated Update Request

DFI PHY-initiated Update Request 是由PHY(物理层)发起的更新请求,目的是为了让PHY更新一些参数,比如延迟线的调整等。uMCTL2(内存控制器)需要响应这些请求并进行相应的处理。

1. DFI PHY-initiated Update Request的应答

- DFI规定了4种不同的PHY发起更新请求模式,每种模式的不同之处在于更新发生时,DFI接口需要被暂停的周期数。这意味着在处理PHY发起的更新请求时,DFI的命令、读数据和写数据通道会被暂停一段时间。

- 启用PHY发起的更新:通过设置DFIUPD2.dfi_phyupd_en寄存器位来启用或禁用此功能。如果该功能被启用(由软件控制),当PHY发起更新请求时,uMCTL2会尽快将DFI命令、读数据和写数据通道挂起,并在处理过程中驱动

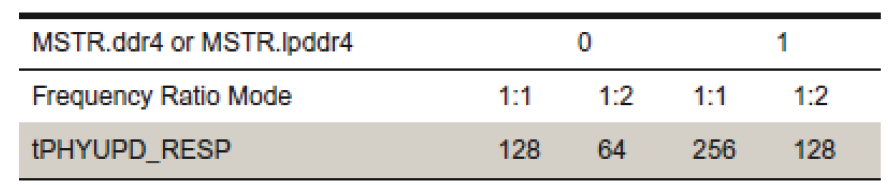

dfi_phyupd_ack信号为高电平,表示uMCTL2已接收到PHY的更新请求并正在处理。- 在1:2频率比模式下,最多暂停64个时钟周期。

- 在1:1频率比模式下,最多暂停128个时钟周期。

2. 冲突避免机制

- dfi_ctrlupd_req和dfi_phyupd_req冲突:有一种情况是dfi_ctrlupd_req(由uMCTL2发起的更新请求)和dfi_phyupd_req(由PHY发起的更新请求)同时被驱动,这可能会导致uMCTL2和PHY同时响应对方的请求,从而违反DFI协议。

- 为了避免这种情况,当dfi_ctrlupd_req和dfi_phyupd_req同时被驱动时,uMCTL2不会对dfi_phyupd_req发出应答(即不驱动

dfi_phyupd_ack为高电平),直到dfi_ctrlupd_req被撤销或完成。这是为了确保uMCTL2不会与PHY同时做出响应,从而防止协议冲突。

3. 刷新与PHY更新的协调

- 如果系统正在使用突发刷新(burst refresh),而同时发生了PHY发起的更新请求,可能会导致tRFCmax(刷新间隔最大时间)违反。这种情况发生在PHY更新请求被发出时,恰好在刷新突发周期之前。为了避免这种情况,uMCTL2会延迟刷新突发的执行,直到PHY更新完成。

- 解决方法:可以通过降低RFSHCTL0.refresh_burst的值来避免这种冲突,这样可以减少刷新突发和PHY更新之间的时间冲突。

4. 时钟移除与PHY更新的时序

- 时钟移除(clock removal)功能:当core_ddrc_core_clk(控制器时钟)从uMCTL2中移除时,DFI接口的时序要求(特别是

tphyupd_resp)可能无法满足。这是因为dfi_phyupd_req = 1信号只有在时钟重新启用后才能被观察到。- tphyupd_resp要求:这意味着在时钟被移除时,dfi_phyupd_req从1到0的过渡及再转回1的过程中,控制器可能无法保证对这些信号的响应。因此,在时钟移除期间,这些PHY发起的更新请求可能无法正确响应。

5. PHY不支持PHY-initiated Updates时的处理

- 如果PHY不支持PHY发起的更新请求,推荐将以下输入设置为0,以禁用该功能:

- DFIUPD2.dfi_phyupd_en = 0,即禁用PHY发起的更新请求。

- phy_ddrc_dfi_phyupd_req = 0,即PHY发起的更新请求信号应为低电平。

- phy_ddrc_dfi_phyupd_type = 00,指定PHY发起的更新类型为“无更新”。

6. tPHYUPD_RESP

- 控制器支持tPHYUPD_RESP值的不同设置,具体来说,这个值是以DFI时钟(控制器时钟)为单位的,表明更新请求的响应时间。

2.7.4 相关寄存器

1. DFIUPD2.dfi_phyupd_en

- 功能:这个寄存器位 (

dfi_phyupd_en) 控制是否启用 DFI PHY-initiated Update Request(由PHY发起的DFI更新请求)。 - 工作原理:如果这个寄存器被设置为

1,则允许PHY发起更新请求,并且uMCTL2需要响应这些请求。当PHY发起更新时,DFI接口的命令、读数据和写数据通道将会被暂停,直到更新完成。这是为了确保PHY更新操作能顺利进行,不会和数据传输产生冲突。 - 用途:在某些情况下,可能希望禁用PHY发起的更新请求(例如,如果控制器和PHY之间有时序或带宽冲突)。在这种情况下,可以将这个寄存器位设置为

0,以禁用PHY发起的更新请求。

2. DFITMG0.dfi_ctrl_delay

- 功能:这个寄存器位 (

dfi_ctrl_delay) 用来设置DFI接口的延迟控制。具体来说,它用于配置 控制器 到 PHY 之间信号的延迟,以确保正确的时序。 - 工作原理:DFI接口需要在适当的时间点进行更新,以确保数据传输的稳定性和准确性。通过设置

dfi_ctrl_delay,可以调整控制器发送信号到PHY的时间延迟,从而优化信号传输的时序,避免出现时序错误或冲突。 - 用途:此寄存器常常用于调整和优化时序,特别是在控制器和PHY之间的信号传递存在时延的情况下。它有助于确保控制信号和数据传输在适当的时刻同步,从而保证系统的稳定性和性能。

3. 参考资料

- 手册中提到,关于这些寄存器的更多详细信息可以在 “Register Descriptions” 部分找到,具体位置是在第717页。在这部分内容中,会对这些寄存器的位字段、默认值、设置范围以及它们的影响等进行更详细的说明。

本文链接: https://talent-tudou.github.io/2024/12/14/DDR/uMCTL2-DFI Updates/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!