2.35.1 片上奇偶校验概述(Overview of On-chip Parity)

数据路径保护

- 在 uMCTL2(即DDR控制器)中,所有的 数据路径 都使用 奇偶校验(Parity) 进行保护。这意味着在数据从一个端点到另一个端点的传输过程中,奇偶校验可以帮助检测到数据中的错误。

- 地址路径保护:地址路径(如AXI接口的地址输入)也通过奇偶校验进行保护。

- 奇偶校验的功能:奇偶校验的作用是能够检测数据中的 奇数个错误。如果发生错误,奇偶校验可以发现问题,但不能确定错误的具体位置,也不能修复错误。

与ECC的关系

- 虽然 ECC(错误更正码) 和 奇偶校验 都是用于提供保护的机制,它们实际上是 独立 启用的。也就是说,你可以单独启用ECC或奇偶校验,或者同时启用。

- 但如果 启用奇偶校验而禁用ECC,则某些奇偶校验功能可能无法使用。因为ECC能够纠正错误,而奇偶校验仅能检测错误,不能进行修正。

支持的配置

- 奇偶校验的功能仅在 AXI配置 中支持。这意味着,只有在AXI接口的配置中,才可以使用奇偶校验来保护数据传输。

片上奇偶校验的架构

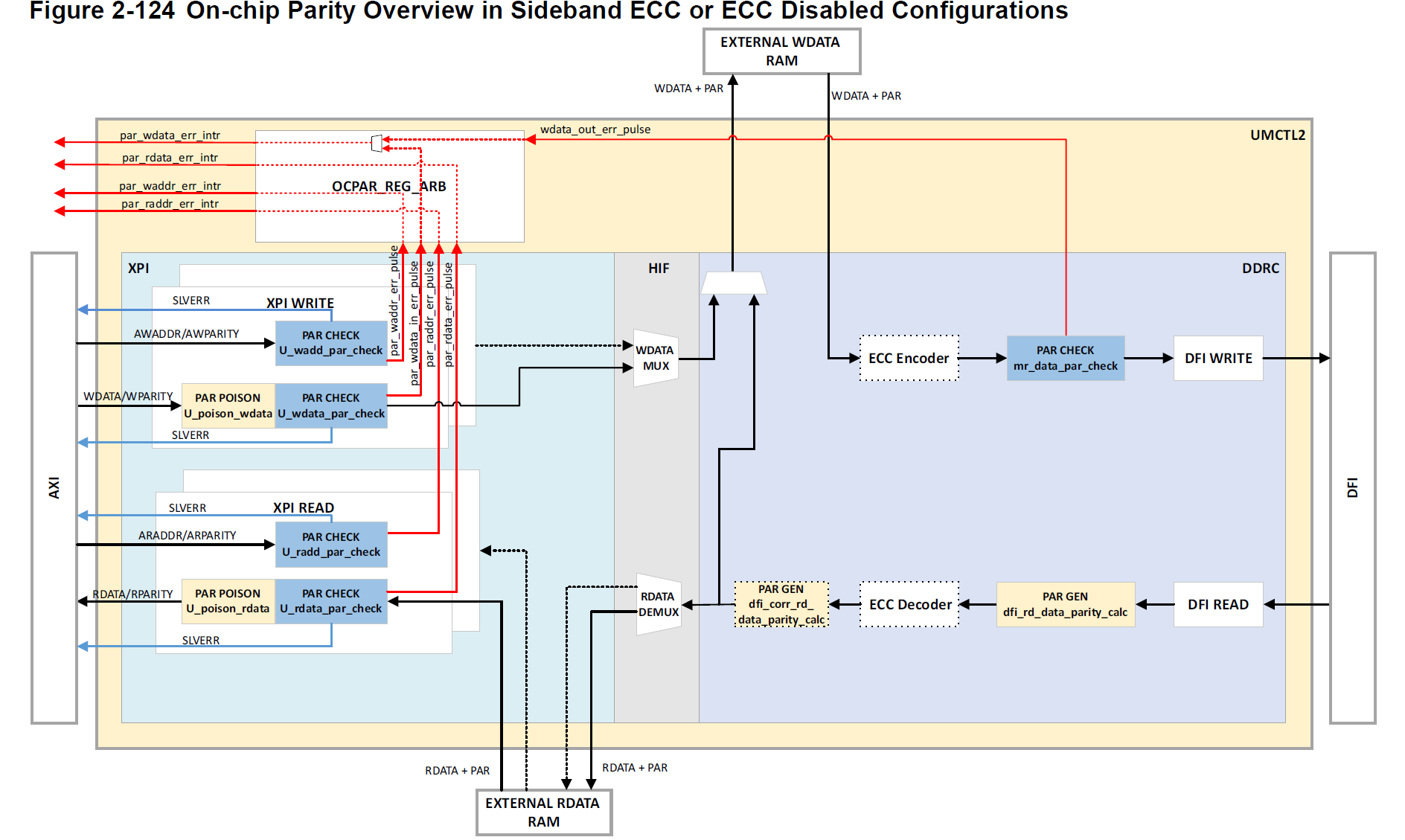

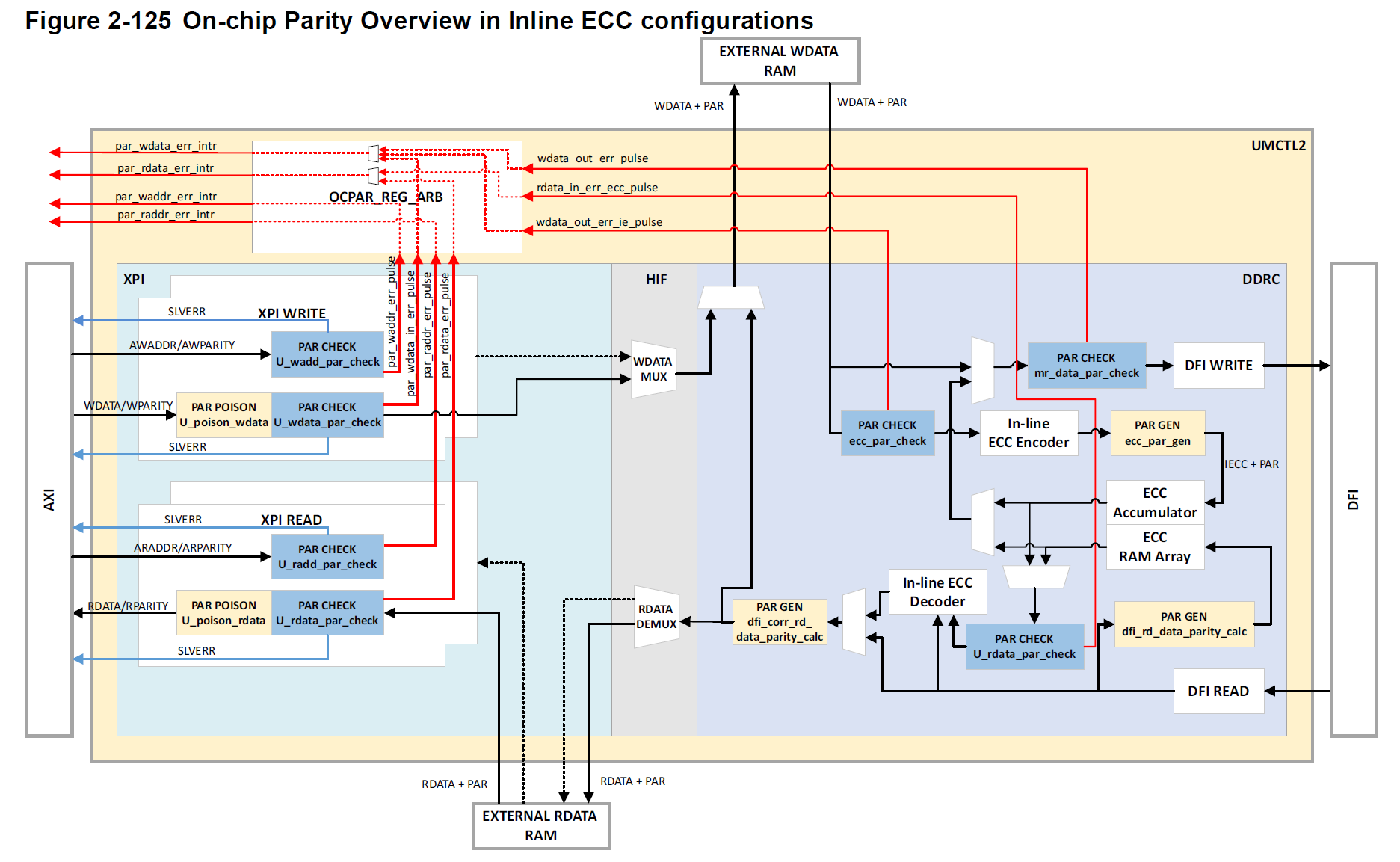

手册中提到的两个图(图 2-124 和图 2-125)展示了不同配置下的片上奇偶校验架构:

- 图 2-124:这是在 边带ECC配置(sideband ECC configurations)下的架构,或在没有ECC支持的配置下(

MEMC_ECC_SUPPORT = 0)。边带ECC配置是指ECC功能并不直接嵌入到内存控制器内,而是以辅助方式工作。

- 在这个架构中,虚线框内的部分 仅在启用了ECC配置时出现(即

MEMC_ECC_SUPPORT > 0)。这些虚线框的部分与ECC的处理机制相关,表示在启用ECC时,数据路径的保护和错误检测会有额外的机制。

- 图 2-125:这是在 内联ECC配置(Inline ECC configurations)下的架构(即

MEMC_INLINE_ECC = 1)。内联ECC是指ECC功能被直接嵌入到内存控制器中,提供更高效的错误检测和修正。

- 内联ECC配置意味着ECC和奇偶校验共同工作,并且ECC机制是内嵌到内存控制器中的。

- 奇偶校验注入(Parity Poisoning)

- 奇偶校验注入(Parity Poisoning) 是指通过在控制器内部注入错误来测试和模拟错误的检测。手册中提到,在DDR控制器(DDRC)块内,每个奇偶校验生成块(PAR GEN)之后 都会存在奇偶校验注入的机制(Parity Poisoning)。

- 这意味着,奇偶校验生成模块会生成校验信息,之后会模拟错误来测试系统对奇偶校验错误的响应。

2.35.2 写数据奇偶校验(Write Data Parity)

1. 奇偶校验的传输

- 每一个 写数据(Write Data)传输周期,都有一个 奇偶校验位 被附加在每一个字节上。这是通过一个称为

wparity_n的边带信号传输的,具体来说,wparity_n[UMCTL2_PORT_NBYTES_n-1:0],它包含了每个字节的数据奇偶校验。 - 这意味着,在 AXI 接口进行数据传输时,除了传送实际的数据外,系统还会附带一个奇偶校验位,用来检测数据传输中的错误。

2. 奇偶校验检查的位置

- 奇偶校验检查会在 两个地方进行:

- AXI 接口后:当数据从 AXI 接口进入到内存控制器时,奇偶校验会首先进行检查。

- DFI 接口前和ECC编码器后:在数据进入 DFI 接口 之前和经过 ECC 编码器 后,还会进行一次奇偶校验检查。

3. 绕过检查

- 如果需要,可以通过 OCPARCFG0.par_wdata_axi_check_bypass_en 寄存器使得 AXI 接口后的奇偶校验检查 被绕过。具体来说,当这个寄存器被设置为

1时,AXI接口后的奇偶校验检查就会被跳过。

4. 错误检测与中断

- 当检测到写数据奇偶校验错误时,会生成一个 可屏蔽的中断信号(

par_wdata_err_intr),这个中断可以通过 OCPARCFG0.par_wdata_err_intr_en 寄存器禁用。 - OCPARSTAT1.par_wdata_err_intr[15:0] 寄存器用于记录哪些 AXI 端口发生了奇偶校验错误。

- OCPARSTAT2.par_wdata_out_err_intr[0] 寄存器用于记录是否在 DFI 接口发生了错误。

5. DFI 接口的额外检查

- 如果启用了 内联 ECC(Inline ECC)(即

MEMC_INLINE_ECC = 1),在 DFI 接口处会进行额外的奇偶校验检查,特别是在 ECC 编码器之前。当检测到奇偶校验错误时,会通过 par_wdata_err_intr_n 中断信号通知。 - OCPARSTAT2.par_wdata_out_err_intr[1:0] 寄存器会记录错误来源:如果是数据路径(bit 0)还是 ECC 路径(bit 1)引起的错误。

6. AXI 接口上的奇偶校验错误响应

- 当 AXI 接口发生写数据奇偶校验错误时,AXI 写响应通道会返回一个 SLVERR(Slave Error) 响应,这表明发生了错误。这个响应会根据 AXI 接口后的奇偶校验检查 是否被绕过而决定。

- 如果 AXI 接口后的检查没有被绕过(即

OCPARCFG0.par_wdata_axi_check_bypass_en = 0),则会产生 SLVERR 响应。 - 对于通过 DFI 接口 检测到的奇偶校验错误,不会通过 SLVERR 响应来通知,而是通过 par_wdata_err_intr 中断信号来通知。该中断信号也可以通过寄存器 OCPARCFG0.par_wdata_err_intr_en 禁用。

7. ECC 影响

- 如果 ECC 被启用(

ECCCFG0.ecc_mode > 0),并且在 DFI 接口 发生了写数据奇偶校验错误,那么相应的 ECC 校验位 就会被破坏。这意味着发生了奇偶校验错误后,ECC 对应的错误校验功能无法正常工作。 - 写地址已提交到内存,但 写数据没有被屏蔽,这意味着即使发生了奇偶校验错误,数据依然会被写入内存。此时需要系统通过 软件 来重新尝试写入正确的数据。

2.35.2.1 输出检查(Output Check)

- ECC 和奇偶校验是互相重叠的保护机制,即它们共同工作来提供数据保护:

- ECC 编码器 首先对数据进行编码(计算 ECC 校验码)。

- 然后,奇偶校验 对已经经过 ECC 编码的数据进行检查。

- 为了确保两者的重叠有效,ECC 编码器和奇偶校验检查之间是通过一个 流水线(pipeline) 来分开的。这是为了保证在 ECC 和奇偶校验之间不会出现冲突或错误。

2.35.2.2 输入检查(Input Check)

- 写数据的 输入奇偶校验检查 发生在 AXI 接口,当

wvalid_n和wready_n信号都处于激活状态时进行。这意味着在数据传输到控制器之前,AXI 接口会进行奇偶校验检查。 - 这种检查确保了所有来自 控制器外部的上游逻辑 的数据都能得到保护。

- 奇偶校验的状态会与 写指针 一起传送,并用于生成 响应。每个数据传输周期(bead)都会附加一个奇偶校验位,以确保数据的正确性。

2.35.3 读数据奇偶校验(Read Data Parity)

1. 奇偶校验生成与传输

- 在 读数据(Read Data)传输过程中,uMCTL2 会为每个字节生成一个奇偶校验位。这些读数据的奇偶校验位会通过 边带信号

rparity_n[UMCTL2_PORT_NBYTES_n-1:0]进行传输。 - 每个读数据周期都会附带一个奇偶校验位,以便在数据传输过程中进行错误检测。

2. 奇偶校验检查的位置

- 读数据的奇偶校验首先在 AXI 接口 进行检查。这意味着,当数据从内存控制器(uMCTL2)通过 AXI 接口返回给主设备时,首先会进行奇偶校验验证。

- 如果检测到奇偶校验错误,控制器会生成 SLVERR 响应信号,表示发生了错误。此响应信号可以通过 OCPARCFG0.par_rdata_slverr_en 寄存器禁用。

3. 错误中断与寄存器

- 除了 SLVERR 响应外,读数据奇偶校验错误还会触发一个 可屏蔽的中断(

par_rdata_err_intr)。这个中断也可以通过 OCPARCFG0.par_rdata_err_intr_en 寄存器进行禁用。 - OCPARSTAT1.par_rdata_err_intr_n 寄存器记录了在哪些 AXI 端口上发生了奇偶校验错误。

2.35.3.1 奇偶校验生成(Parity Generation)

- 读数据的奇偶校验生成与 ECC 解码器 在同一个流水线阶段生成,这意味着它们是共享一个流水线的。

- 图 2-126 展示了这种奇偶校验和 ECC 的重叠保护机制。在这个设计中,奇偶校验和 ECC 会一起工作,从而提供更强的数据保护。

2.35.3.2 奇偶校验检查(Parity Check)

- 读数据的奇偶校验检查会在 AXI 接口 进行,具体来说,当

rvalid_n信号激活时,会触发检查。 - 如果启用了 内联 ECC(Inline ECC),那么除了 AXI 接口处的奇偶校验检查外,还会在 DFI 接口 进行额外的检查。此检查发生在 ECC 解码器之前,目的是保护 ECC 字(ECC word)——这部分数据与实际的读数据分开传输。

- 如果在 DFI 接口检测到奇偶校验错误,会通过 par_rdata_err_intr 中断信号触发,并更新 OCPARSTAT2.par_rdata_in_err_ecc_intr 寄存器。

2.35.3.3 地址奇偶校验(Address Parity)

- AXI 地址(araddr 和 awaddr)也有奇偶校验保护,可以通过两种方式进行保护:

- 一种是为整个地址提供一个奇偶校验位。

- 另一种是为每个地址字节提供一个奇偶校验位,具体方式由硬件参数 UMCTL2_OCPAR_ADDR_PARITY_WIDTH 决定。

- 地址的奇偶校验通过 边带信号

arparity/awparity传输。 - 地址奇偶校验的检查会在 XPI 接口 内部进行,当

awready_n == 1和awvalid == 1时进行写地址的奇偶校验检查;同样,当arready_n == 1和arvalid_n == 1时,会对读地址进行奇偶校验检查。 - 地址奇偶校验错误会通过 AXI SLVERR 响应 通知主设备。此错误响应可以通过 OCPARCFG0.par_addr_slverr_en 寄存器禁用。

- 错误中断与寄存器:

- 除了 SLVERR 错误响应外,地址奇偶校验错误还会生成两个 可屏蔽的中断,分别用于写地址错误(

par_waddr_err_intr)和读地址错误(par_raddr_err_intr)。 - 这些中断可以通过 OCPARCFG0.par_waddr_err_intr_en 和 OCPARCFG0.par_raddr_err_intr_en 寄存器禁用。

- OCPARSTAT0.par_waddr_err_intr[15:0] 和 OCPARSTAT0.par_raddr_err_intr[15:0] 寄存器记录了发生地址奇偶校验错误的 AXI 端口。

- 除了 SLVERR 错误响应外,地址奇偶校验错误还会生成两个 可屏蔽的中断,分别用于写地址错误(

- 地址奇偶校验的“事务污染”:

- 地址奇偶校验错误会导致 地址污染(Address Poisoning),这意味着如果发生了地址奇偶校验错误,控制器会把该地址标记为有问题,类似于 事务污染 的处理。之后,该地址会被当作无效地址进行处理。

2.35.3.4 嵌入式 SRAM 保护(Embedded SRAM Protection)

- 对于外部 SRAM(静态随机存取内存)接口,控制器提供了 数据和字节的奇偶校验:

- 写数据和读数据的奇偶校验会被传送到外部 SRAM,并且控制器不进行对这些输出的检查。控制器仅提供数据和对应的奇偶校验信号。

- 需要通过外部硬件驱动将正确的奇偶校验位传输给控制器。

- 具体的奇偶校验信号包括:

- wdataram_din_par:写数据输入的奇偶校验。

- rdataram_din_par_n:读数据输入的奇偶校验。

- wdataram_dout_par:写数据输出的奇偶校验。

- rdataram_dout_par_n:读数据输出的奇偶校验。

- 如果某个外部端口未启用,奇偶校验会保存在 内部寄存器 中,无需外部处理。

2.35.3.5 读修改写操作(Read Modify Write Operation)

- 读修改写(RMW)操作需要同时通过读路径和写路径。由于这两条路径都有奇偶校验保护,因此 RMW 操作会得到适当的保护。

- 如果在读路径上发生了无法纠正的 ECC 错误,那么读数据的奇偶校验会被破坏(这取决于寄存器的设置)。这将导致写路径上的 ECC 校验位 也被破坏。

- 如果奇偶校验未启用,控制器在检测到无法纠正的 ECC 错误时,仍然会直接破坏写路径上的 ECC 校验。

2.35.3.6 Parity Poisoning(奇偶校验污染)

启用奇偶校验污染功能:

- 奇偶校验污染功能可以通过设置寄存器 OCPARCFG1.par_poison_en 来启用(详细信息见UMCTL2_REGS寄存器表)。

- 一旦启用,控制器可以在不同的 数据路径(例如读数据路径或写数据路径)中注入奇偶校验错误,来测试系统如何响应这些错误。

注入位置:

- 奇偶校验错误可以在以下数据接口中注入,可以任意组合使用:

读数据路径中的奇偶校验污染:

- DFI 接口:奇偶校验错误可以在数据从 DFI 接口生成后被注入,这个位置通过设置寄存器 OCPARCFG1.par_poison_loc_rd_dfi 来控制。

- 内联 ECC(Inline ECC)模式:如果启用了内联 ECC,那么数据可以沿两条路径之一传输(数据路径或 ECC 路径)。可以通过寄存器 OCAPRCFG1.par_poison_loc_rd_iecc_type 来选择在哪条路径上注入奇偶校验错误。

- 为了确保污染的数据能够传递到 AXI 接口并被检测到,必须 禁用所有自动 MR 命令,并通过设置寄存器 DERATEEN.derate_enable 为 ‘0’ 来禁用自动温度衰减功能。

AXI 接口中的读数据奇偶校验错误:

- 在 AXI 接口中,奇偶校验错误可以在 读数据检查之后 注入,且只能一次性注入到一个端口。这一操作通过设置寄存器 OCPARCFG1.par_poison_loc_rd_port 来启用。

- 控制器不会捕获这些注入的错误。

写数据路径中的奇偶校验污染:

- 奇偶校验错误可以在 AXI 接口写数据检查之前 注入,并且只能一次性注入到一个端口。这通过寄存器 OCPARCFG1.par_poison_loc_wr_port 来控制。

- 如果 AXI 检查器没有旁路(即寄存器 OCPARCFG0.par_wdata_axi_check_bypass_en 设置为 0),则会在写数据路径的 AXI 接口注入奇偶校验错误。如果 AXI 检查器旁路(设置为 1),则不会注入奇偶校验错误。

一次性触发(One-shot triggering):

- 一次性触发意味着奇偶校验错误只会在首次有效的数据传输时注入,这发生在 OCPARCFG1.par_poison_en 被设置为

1或中断清除信号被触发之后。 - 这意味着奇偶校验错误只会注入到第一次传输的

DFI事务的 第一拍(beat) 上。

- 一次性触发意味着奇偶校验错误只会在首次有效的数据传输时注入,这发生在 OCPARCFG1.par_poison_en 被设置为

清除中断并重新启用奇偶校验污染:

- 如果奇偶校验错误中断被触发,可以通过设置 OCPARCFG0.par_wdata_err_intr_clr 来重新启用写数据路径上的奇偶校验污染。

- 通过设置 OCPARCFG0.par_rdata_err_intr_clr 来重新启用读数据路径上的奇偶校验污染。

AXI 交通限制:

- 对于在控制器上启用的 奇偶校验污染功能,有几个 AXI 交通限制,确保系统的可靠性和正确性:

- AXI burst 类型必须为 INCR。

- AXI 地址必须对齐到 SDRAM burst 的边界(关于 AXI 到 SDRAM 地址映射的更多信息可以参考“Address Mapper”章节)。

- AXI 地址不能访问无效的 LPDDR3/LPDDR4 行地址。

- AXI 写突发(Write Burst)不能在 HIF 上执行读写修改(RMW)操作。

- AXI 地址必须对齐到 INLINE_ECC 块的边界。

- 单个 AXI 事务不能跨越多个 ECC 区域/块。

- 如果启用了 内联 ECC(Inline ECC) 模式,则为了确保污染数据能够到达 AXI 并被检测到,AXI 必须执行读访问到所有被 AXI 写入的 DDR 控制器内存位置,在启用污染之后。

- 对于在控制器上启用的 奇偶校验污染功能,有几个 AXI 交通限制,确保系统的可靠性和正确性:

总线宽度限制:

- 所有上述的 AXI 交通限制仅适用于 全总线宽模式(full bus width mode),这取决于控制器的 MSTR.data_bus_width 设置。如果控制器工作在半总线宽或四分之一总线宽模式下,奇偶校验污染功能将不可用。

2.35.4 启用内部奇偶校验功能(Enabling On-chip Parity)

这部分描述了如何在配置 uMCTL2 DDR 控制器 时启用内部奇偶校验功能。具体方法是:

- 打开 coreConsultant GUI(通常是配置和管理 uMCTL2 控制器的图形化工具)。

- 在图形界面中找到 Reliability Features/RAS Specific Configuration Options(可靠性特性/容错特定配置选项)部分。

- 选择 Enable On-chip Parity feature(启用内部奇偶校验功能)选项来启用此功能。

内部奇偶校验功能是在控制器内自动进行的,主要用于监测和纠正传输过程中的数据错误。启用该功能后,控制器会对数据进行奇偶校验,从而确保数据的完整性和正确性。

2.35.5 与内部奇偶校验相关的信号(Signals Related to On-chip Parity)

此部分提到了与 内部奇偶校验 相关的一些信号,具体是:

- AXI Port n Write Address On-Chip Parity Signals:与 AXI 接口写地址的奇偶校验信号相关。

- AXI Port n Read Address On-Chip Parity Signals:与 AXI 接口读地址的奇偶校验信号相关。

这些信号用于监测和传输数据的奇偶校验值。例如,当数据通过 AXI 总线进行传输时,这些信号确保数据在传输过程中没有发生错误。如果有错误,控制器会在这些信号中检测到异常,并做出相应的响应。

更详细的信息,可以查看手册中后面的章节:

- “AXI Port n Write Address On-Chip Parity Signals” 章节(第550页);

- “AXI Port n Read Address On-Chip Parity Signals” 章节(第562页)。

2.35.6 与内部奇偶校验相关的寄存器(Registers Related to On-chip Parity)

这部分列出了与内部奇偶校验相关的寄存器:

- OCPARCFG0:配置寄存器,包含奇偶校验功能的启用和配置选项。

- OCPARCFG1:另一个配置寄存器,控制更详细的奇偶校验行为。

- OCPARSTAT0:状态寄存器,用于监控奇偶校验相关的状态。

- OCPARSTAT1:另一个状态寄存器,用于记录奇偶校验错误和其他相关信息。

- OCPARSTAT2:进一步的状态寄存器,可能涉及其他高级错误或状态记录。

要详细了解这些寄存器的功能和配置方法,可以参考手册中的 “Register Descriptions” 章节(第717页)。这些寄存器允许用户对奇偶校验功能进行精确配置和监控,确保在发生错误时能够及时检测和响应。

本文链接: https://talent-tudou.github.io/2024/12/13/DDR/uMCTL2-On-chip Parity (OCPAR)/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!