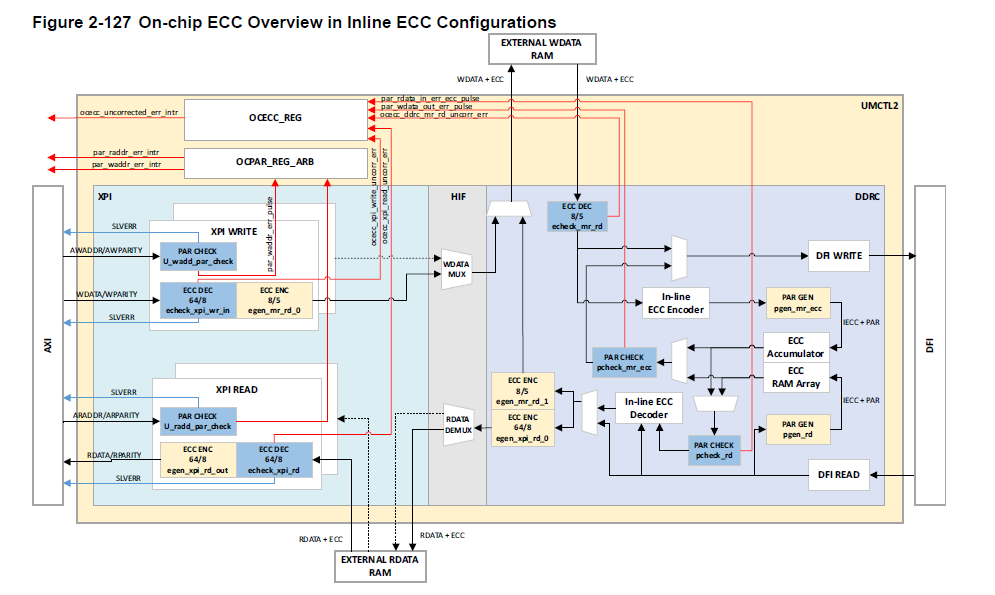

2.36.1 Overview of On-chip ECC

1. ECC与奇偶校验的区别

- ECC (Error Correcting Code):是一种错误检测和修正技术,能够检测并修正数据传输中的单比特错误,甚至能够检测到多比特错误。ECC比奇偶校验(Parity)更为强大,因为它不仅能检测错误,还能尝试修正错误。

- 奇偶校验(Parity):是一种简单的错误检测技术,只能检测错误,不能修正。它通常使用一个额外的位来表示数据中1的个数是奇数还是偶数。如果数据传输过程中发生了错误,这个奇偶校验位就会发生变化,表明数据发生了错误。

2. On-chip ECC的描述

On-chip ECC:是在数据路径中使用ECC来代替传统的奇偶校验。该技术特别适用于汽车产品(AP)许可证持有者,并且为数据路径中的某些部分提供更强的错误保护。具体来说,On-chip ECC在数据传输过程中采用不同的ECC技术来保护数据。

64/8 ECC、8/5 ECC:这些是ECC的不同配置,指的是用来保护数据的编码方式和数据位数的比例。

每字节偶校验(per-byte even parity):在某些部分,尽管使用了ECC技术,但依然保留了传统的偶校验来确保兼容性和简化设计。

On-chip Address Parity:这是另一种地址奇偶校验功能,和On-chip ECC一起启用,进一步提高了对地址线的保护。

3. 工作原理

- ECC与数据一起传输:在传输过程中,ECC代码与数据一起传输,并在数据重新排列时进行重新计算。这意味着如果数据的位置发生了变化,ECC也会随之更新。

- 奇偶校验与ECC交替使用:在一些复杂的设计中,虽然大部分数据路径使用了ECC,但某些部分由于设计复杂性仍然保持了奇偶校验。这些部分的奇偶校验使用的是“偶校验”。

4. 错误检测与中断

- 错误检测:当ECC或奇偶校验被终止时,控制器会检查数据中是否发生了错误。如果检测到错误,控制器会触发一个中断。

- 错误类型

- 单比特错误:ECC解码器不会尝试修正单比特错误(这通常是硬件设计的限制,意味着它只能检测,但不能修正)。

- 多比特错误或奇数比特错误:如果在同一数据字(ECC数据单元)中检测到两个或多个比特错误,或者检测到奇数个比特错误,控制器会生成中断并报告错误。

- 奇偶校验错误:如果奇偶校验发生错误,控制器也会触发中断。

5. 支持条件

- AXI配置和内联ECC:这个功能(片上ecc)仅在支持AXI(高级扩展接口)配置的设计中启用,并且需要支持内联ECC(即ECC和数据一起进行处理)。

2.36.1.1 ECC Encoding

1. ECC算法

- SECDED Hamming (72,64) Code:这里使用的是一种Hamming代码,即SECDED(Single Error Correct Double Error Detect)算法,这是一种常用的错误检测和修正码。具体来说,(72,64)指的是:

- 64位数据被编码成72位数据,其中包括64位原始数据和8位ECC位。

- 这种编码方案可以:

- 修正单比特错误(Single Error Correct)。

- 检测到双比特错误(Double Error Detect)。

SECDED是一种广泛使用的ECC算法,因为它不仅能够修正单比特错误,还能检测到多比特错误(最多双比特错误)。

2. ECC编码器与解码器的实现

- 编码器(OCECC Encoder):

- 编码器的实现文件在以下路径:

src/ocecc/ocecc_enc.vsrc/mr/mr_secded_lane.v

- 编码器的作用是将64位数据转化为带有ECC的72位数据。

- 编码器的实现文件在以下路径:

- 解码器(OCECC Decoder):

- 解码器的实现文件在以下路径:

src/ocecc/ocecc_dec.vsrc/rd/rd_secded_lane.v

- 解码器的作用是接收72位的ECC编码数据,并检查是否存在错误。如果有单比特错误,解码器会尝试修正它;如果是双比特错误,则会报告错误但不做修正。

- 解码器的实现文件在以下路径:

3. AXI接口上的ECC编码

64/8 ECC:在AXI接口上使用的是

64/8 ECC编码。这意味着:

- 每64位的数据需要8个ECC位。

- 如果AXI数据总线宽度是128位,那么你需要提供两个8位的ECC字,以保证每64位数据都能进行ECC保护。

外部写数据RAM上的ECC编码(8/5):对于外部写数据的RAM,使用的是8/5的ECC编码。具体来说,这是指每8位数据有5个ECC位。

4. AXI接口的数据宽度要求

- 最小数据宽度为64位:AXI接口至少支持64位宽度的数据传输,也就是说,每次数据传输最小为64位。

- 写数据通道上的ECC要求:

- AXI主设备(AXI Master)必须为每64位的AXI写数据提供正确的ECC。这包括了在AXI写数据通道上传输的数据字节,即使某些字节的写使能(strobe)为零,或者进行的是AXI子尺寸传输,也要提供相应的ECC。

- 例如,如果AXI传输宽度是128位,主设备必须提供两个64位的ECC数据;如果传输的是子尺寸(例如64位或者32位),也必须为每个64位的写数据提供相应的ECC。

2.36.1.2 写数据保护

- 写数据的ECC保护:

- 对于每个写数据周期(write data beat),uMCTL2(DDR控制器)会为每64位的数据提供一个8位的ECC字。换句话说,每64位的写数据都会伴随一个8位的ECC进行传输。

- 这些ECC数据通过一个旁路信号(sideband signal)叫做wparity_n来传输。

wparity_n信号的宽度由UMCTL2_PORT_NBYTES_n-1:0定义。

- ECC校验:

- ECC的校验在两个地方进行:

- AXI接口:当写数据有效(

wvalid_n == 1)并且控制器准备好接收数据(wready_n == 1)时,进行ECC检查。 - 外部写数据RAM:当数据被写入外部内存时,再次进行ECC校验。

- AXI接口:当写数据有效(

- ECC的校验在两个地方进行:

- 奇偶校验:

- 在内联ECC编码器之后,会使用奇偶校验(parity)代替ECC进行保护。奇偶校验会在DFI接口之前进行检查。

- AXI接口上的写事务处理:

- 如果在AXI接口上检测到写数据的ECC错误,AXI响应通道会返回SLVERR(Slave Error)响应。SLVERR响应表示发生了错误,控制器未能成功完成写操作。

- 注意:uMCTL2将所有的AXI事务视为可缓存的(bufferable),无论事务的属性如何。这意味着,写响应是在最后一个写数据周期被接受时生成的,通常在DDR控制器的CAM(内容寻址存储器)内部完成。

- SLVERR响应只会在AXI接口上的ECC校验失败时生成。

- 如果需要禁用SLVERR响应,可以通过

OCECCCFG0.ocecc_wdata_slverr_en进行配置。

- 错误日志:

OCECCSTAT1.ocecc_err_xpi_wr_in_n寄存器用于记录检测到写数据ECC错误的AXI端口。

2.36.1.3 读数据保护

- 读数据的ECC保护:

- 对于每个读数据周期(read data beat),uMCTL2会为每64位的读数据提供一个8位的ECC字。读数据ECC通过旁路信号rparity_n传输,信号宽度同样由

UMCTL2_PORT_NBYTES_n-1:0定义。

- 对于每个读数据周期(read data beat),uMCTL2会为每64位的读数据提供一个8位的ECC字。读数据ECC通过旁路信号rparity_n传输,信号宽度同样由

- ECC校验:

- ECC在AXI接口处进行校验,校验条件是读数据有效(

rvalid_n == 1)时进行。

- ECC在AXI接口处进行校验,校验条件是读数据有效(

- 错误处理:

- 如果在读数据时发生ECC错误,AXI会返回SLVERR响应,表示发生了错误,读数据操作没有成功完成。

- 错误响应的启用或禁用可以通过

OCECCCFG0.ocecc_rdata_slverr_en进行控制。

- 错误日志:

OCECCSTAT1.ocecc_err_xpi_rd_n寄存器用于记录检测到读数据ECC错误的AXI端口。

2.36.1.4 错误检测

- ECC解码器或奇偶校验器中的错误:

- 如果在ECC解码器或奇偶校验器中检测到错误,会触发以下信号:

- 中断信号:

ocecc_uncorrected_err_intr(如果在OCECCCFG0.ocecc_uncorrected_err_intr_en中启用的话)。 - 故障信号:

ocecc_uncorrected_err_intr_fault(无论中断是否启用,都会触发此信号)。 - 错误状态寄存器:

OCECCSTAT0.ocecc_uncorrected_err,用于记录错误信息。

- 中断信号:

- 如果在ECC解码器或奇偶校验器中检测到错误,会触发以下信号:

- 日志记录:

OCECCSTAT2.ocecc_err_ddrc_mr_rd_byte_num寄存器记录在写数据RAM中发生ECC错误时,具体是哪一个字节引发的错误。

- 测试和调试:

- 在测试或调试时,可以通过设置

OCECCCFG0.ocecc_uncorrected_err_intr_force为1来强制触发一个OCECC中断。这意味着系统会模拟一个错误并触发错误处理机制。 - 中断可以通过向

OCECCCFG0.ocecc_uncorrected_err_intr_clr写1来清除。

- 在测试或调试时,可以通过设置

2.36.1.5 地址奇偶校验(Address Parity)

地址奇偶校验简介

- 地址保护:

- 在DDR控制器中,AXI接口的地址(包括读取地址

araddr和写入地址awaddr)通过奇偶校验来进行保护。 - 根据硬件配置参数

UMCTL2_OCPAR_ADDR_PARITY_WIDTH,可以选择两种奇偶校验方式:- 整个地址的奇偶校验:即对整个地址进行单一位的奇偶校验。

- 每个地址字节的奇偶校验:即每个字节的地址都有单独的奇偶校验位。

- 地址奇偶校验通过旁路信号

arparity/awparity传输。

- 在DDR控制器中,AXI接口的地址(包括读取地址

地址奇偶校验检查

- 地址奇偶校验会在XPI模块(Xilinx接口)内进行检查和终止。XPI模块负责处理数据与地址的传输,并对奇偶校验进行验证。

错误响应

- 如果发生地址奇偶校验错误,会通过AXI的SLVERR响应(Slave Error)信号通知主设备(Master),这意味着该地址传输出现了错误。

- SLVERR响应可以通过配置寄存器禁用,例如通过设置

OCPARCFG0.par_addr_slverr_en寄存器来关闭错误响应。

- SLVERR响应可以通过配置寄存器禁用,例如通过设置

地址奇偶校验错误的中断处理

- 除了通过AXI SLVERR响应报告错误外,地址奇偶校验错误还会生成可屏蔽的中断:

- 写地址错误中断:

par_waddr_err_intr。 - 读地址错误中断:

par_raddr_err_intr。 - 这些中断可以通过设置

OCPARCFG0.par_waddr_err_intr_end和OCPARCFG0.par_raddr_err_intr_en来禁用。

- 写地址错误中断:

地址奇偶校验与“事务中毒(Transaction Poisoning)”的关联

- 地址奇偶校验错误会导致“地址中毒(address poisoning)”,这种机制与事务中毒类似。也就是说,出现地址奇偶校验错误的地址会被认为是无效的(即中毒),并且后续对这个地址的操作会受到影响。

错误日志

- 地址奇偶校验错误会在

OCPARSTAT0寄存器中记录,具体包括:par_waddr_err_intr[15:0]:记录写地址的奇偶校验错误。par_raddr_err_intr[15:0]:记录读地址的奇偶校验错误。

2.36.1.6 嵌入式SRAM保护(Embedded SRAM Protection)

外部SRAM接口的数据保护

- 外部SRAM接口:与外部SRAM进行数据交互时,数据和ECC会一起传输。控制器会为数据生成ECC并将其与数据一起传输出去,但在控制器内部并没有进行ECC检查。

数据ECC

- 控制器在数据输出端会生成ECC:

- 写数据ECC:

wdataram_din_par:为写数据RAM输入端(wdataram_din)生成的8位ECC(用于5位数据)。- 读数据ECC:

rdataram_din_par_n:为读数据RAM输入端(rdataram_din_n)生成的64/8 ECC。rdataram_dout_par_n:为读数据RAM输出端(rdataram_dout_n)生成的64/8 ECC。

- 写数据ECC:

外部SRAM和控制器的数据传输

- 当读取外部SRAM的数据时,控制器需要通过ECC来确保数据的完整性。对于每个外部RAM(通过各端口

port n访问的SRAM),ECC的生成和检查是独立的。 - 输入和输出ECC的要求

- 控制器期望每次从SRAM读取数据时,都能正确传入64/8 ECC,确保读取的数据无错误。

- 如果外部RAM支持多个端口,每个端口会有自己的ECC信号。

ECC的内部处理

- 如果某个外部RAM端口(

port n)没有启用,相关的ECC数据就会被存储在RRB(读写缓冲区)内,内部RAM会处理这些ECC和数据。此时,用户不需要进行额外的ECC处理。

2.36.1.7 ECC/Parity Poisoning(ECC/奇偶校验注入错误)

概述:

- ECC Poisoning(ECC错误注入)是一个模拟错误注入的功能,用于测试ECC编码器和奇偶校验生成器在错误情况下的工作表现。当启用此功能时,控制器可以故意注入ECC错误或奇偶校验错误,进而验证系统如何处理这些错误。

- 这个功能通过设置**

OCECCCFG1.ocecc_poison_en**寄存器来启用。

允许注入错误的编码器:

这部分列举了可以进行注入错误的ECC编码器和奇偶校验生成器:

- egen_mr_rd_0:这个编码器负责读取地址的ECC处理。通过设置**

OCECCCFG1.ocecc_poison_egen_mr_rd_0**寄存器来启用注入。可以选择哪个字节会被注入错误(OCECCCFG1.ocecc_poison_egen_mr_rd_0_byte_num),并且可以选择是否注入1位或2位错误(OCECCCFG1.ocecc_poison_ecc_corr_uncorr)。 - egen_mr_rd_1:这个编码器负责另一组读取地址的ECC处理。类似于

egen_mr_rd_0,它也通过设置寄存器来启用错误注入,并可以选择注入错误的字节和错误类型(1位或2位)。 - egen_xpi_rd_0:这个编码器负责XPI接口的读取数据的ECC。错误注入也可以通过寄存器启用,并选择错误的类型。

- egen_xpi_rd_out:这个编码器负责XPI接口的输出数据的ECC。错误注入的启用方式和上述类似。

- pgen_mr_ecc:这是一个负责生成写地址ECC的奇偶校验生成器,通过设置相应的寄存器启用错误注入。

- pgen_rd:这是一个负责生成读取地址ECC的奇偶校验生成器,同样可以通过寄存器启用错误注入。

错误注入的操作:

- 一键式注入(One-shot Poisoning):

- 错误注入的机制是“一键式”的,也就是说,一旦启用错误注入,它会在接下来第一次有效的数据传输时注入错误。

- 错误注入会在

OCECCCFG1.ocecc_poison_en寄存器被设置为1时开始,或者在清除中断(OCECCCFG0.ocecc_uncorrected_err_intr_clr)后开始。

错误注入的影响

- 注入ECC错误或奇偶校验错误后,对应的ECC解码器或奇偶校验检查器会检测到错误并做出响应。

- 注入错误之后,系统会模拟正常的ECC或奇偶校验错误的处理流程,如错误响应、修正或触发中断等。

AXI流量限制(AXI Traffic Restrictions)

要启用ECC/奇偶校验错误注入,存在一些AXI流量限制,即在执行注入错误时,AXI总线的流量必须满足特定的要求:

- AXI突发类型必须是INCR:只能进行增量突发(INCR)类型的传输,不能使用其他类型(如Wrap等)。

- AXI地址必须与SDRAM突发对齐:即AXI地址必须与SDRAM的突发(burst)对齐。

- AXI地址不能访问无效的LPDDR3/LPDDR4行地址:即只能访问有效的内存区域。

- AXI地址必须与Inline ECC块对齐:如果启用了Inline ECC(

MEMC_INLINE_ECC == 1),AXI地址必须对齐到ECC块的边界。 - AXI事务不能访问多个ECC区域/块:在Inline ECC模式下,AXI事务不能跨越多个ECC区域或块。

- 特殊AXI写操作要求:在Inline ECC模式下,如果对

egen_mr_rd_1块进行错误注入,AXI写突发必须触发读-修改-写(RMW)操作。对于其他块(除了egen_mr_rd_1),AXI写突发不能触发RMW。

AXI总线宽度限制:

- 这个错误注入功能仅在全总线宽度模式下有效。如果使用的是半总线宽度或四分之一总线宽度(half/quarter bus width),则ECC/奇偶校验错误注入功能不支持。

2.36.2 启用片上ECC支持(Enabling On-chip ECC Support)

1. 启用On-chip ECC的方式:

核心配置工具(coreConsultant GUI)配置:

- 在使用核心配置工具(如coreConsultant GUI)配置DDR控制器时,可以通过选择

Enable On-chip ECC选项来启用片上ECC支持。这是通过设置硬件参数UMCTL2_OCECC_EN来完成的。该选项通常位于 Reliability Features 部分的 On-chip Reliability 子部分中。

这意味着在图形化工具中配置时,用户可以通过勾选一个选项来启用片上ECC功能。

- 在使用核心配置工具(如coreConsultant GUI)配置DDR控制器时,可以通过选择

软件配置:

- 在硬件配置之后,片上ECC支持的启用/禁用可以通过软件控制。具体来说,软件通过设置寄存器

OCECCCFG0.ocecc_en来启用或禁用片上ECC功能。- 例如,设置

OCECCCFG0.ocecc_en = 1表示启用片上ECC。 - 设置

OCECCCFG0.ocecc_en = 0表示禁用片上ECC。

- 例如,设置

- 在硬件配置之后,片上ECC支持的启用/禁用可以通过软件控制。具体来说,软件通过设置寄存器

2. 启用On-chip地址奇偶校验(Address Parity):

- On-chip 地址奇偶校验 也是一个与片上ECC相关的功能,可以通过软件控制启用或禁用。具体通过设置寄存器

OCPARCFG0.oc_parity_en来启用或禁用地址奇偶校验功能。

3. 注意事项:Scrubber模式下的限制:

- Scrubber功能与片上ECC的冲突:

- Scrubber 是一种用于数据清洗(或错误清除)的功能,它可以对DDR内存进行操作以修复错误。在手册中提到,如果启用了Scrubber(即

UMCTL2_SBR_EN被定义为1),并且Scrubber处于写模式(SBRCTL.scrub_en = 1且SBRCTL.scrub_mode = 1),则片上ECC的检查器不可用。 - 为什么需要禁用片上ECC?

- 在Scrubber的写模式下,片上ECC的检查器可能与Scrubber的写操作发生冲突。因此,在Scrubber处于写模式时,必须禁用片上ECC功能。否则,ECC检查器无法正常工作,可能导致错误检测和修复失败。

- 如何禁用片上ECC?

- 在Scrubber写模式下,必须通过设置寄存器

OCECCCFG0.ocecc_en = 0来禁用片上ECC。

- 在Scrubber写模式下,必须通过设置寄存器

- 参考手册中更多的内容:

- 关于Scrubber和片上ECC的详细交互以及如何在初始化写操作中正确配置Scrubber和片上ECC,手册的 “ECC Scrubber” 部分有进一步的说明。你可以参考 “ECC Scrubber” 章节中的 “Initialization Writes” 部分,了解更多关于如何正确初始化和配置Scrubber以及片上ECC的详细步骤。

- Scrubber 是一种用于数据清洗(或错误清除)的功能,它可以对DDR内存进行操作以修复错误。在手册中提到,如果启用了Scrubber(即

2.36.3 与片上ECC相关的信号(Signals Related to On-chip ECC)

这部分主要列出了与片上ECC功能相关的信号和它们的详细信息位置,帮助用户了解如何在不同的配置和操作中使用这些信号:

- AXI端口n写数据片上奇偶校验信号(AXI Port n Write Data On-Chip Parity Signals):

- 这些信号涉及到在AXI接口上进行写操作时的数据传输。每个AXI端口(n)会有与之对应的写数据的片上奇偶校验信号。

- 更多信息请参见手册第553页。

- AXI端口n读数据片上奇偶校验信号(AXI Port n Read Data On-Chip Parity Signals):

- 这些信号涉及AXI接口上的读操作。在AXI读操作时,会有与之相关的读数据的片上奇偶校验信号。

- 更多信息请参见手册第565页。

- AXI端口n写地址片上奇偶校验信号(AXI Port n Write Address On-Chip Parity Signals):

- 这些信号与AXI写操作中传输的地址相关。每个AXI端口(n)都有与之相关的写地址的片上奇偶校验信号。

- 更多信息请参见手册第550页。

- AXI端口n读地址片上奇偶校验信号(AXI Port n Read Address On-Chip Parity Signals):

- 这些信号与AXI接口上的读操作传输的地址相关。

- 更多信息请参见手册第562页。

- 片上ECC信号(On-Chip ECC Signals):

- 这部分涵盖了所有与片上ECC相关的信号,描述了如何在DDR控制器中处理ECC功能。

- 更多信息请参见手册第580页。

2.36.4 与片上ECC相关的寄存器(Registers Related to On-chip ECC)

这部分列出了与片上ECC功能相关的寄存器,并提供了寄存器的名称。通过这些寄存器,用户可以配置、控制和查询与ECC相关的各种状态信息。

- OCECCCFG0:

该寄存器用于配置片上ECC的启用/禁用等相关设置,通常是片上ECC功能的控制寄存器之一。 - OCECCCFG1:

该寄存器提供了额外的配置选项,可能与ECC错误注入、错误检测等功能有关。 - OCECCSTAT0、OCECCSTAT1、OCECCSTAT2:

这些寄存器用于显示片上ECC相关的状态信息,可能包括ECC错误、ECC错误的位置、发生的次数等。它们通常用于监控和诊断片上ECC的工作状态。 - OCPARCFG0:

该寄存器配置与地址奇偶校验相关的设置。 - OCPARSTAT0:

该寄存器记录和显示与地址奇偶校验相关的状态信息。

本文链接: https://talent-tudou.github.io/2024/12/13/DDR/uMCTL2-On-chip ECC/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!