pub手册4.6,BIST (Built-In Self-Test) 模块是一种可编程的自检引擎,它为应用程序提供了一种测试 DDR PHY 和 I/O 的方法,主要用于高速生产测试。BIST 模块通过 回路回送(loopback)方式来验证 PHY 的发送路径和接收路径的功能。除此之外,还可以选择测试外部内存的功能。

BIST 模块的功能

- PHY 测试:

BIST 通过将数据从 PHY 的发送路径通过回路回送到接收路径,来测试 PHY 的发送和接收功能。通过此方式,不需要外部存储器即可完成测试。 - I/O 测试:

BIST 还可以测试 I/O 的功能,确保数据能够正确地通过 I/O 接口传输。 - 外部内存测试(可选):

如果需要,BIST 还提供了测试外部内存的功能。此时,BIST 会发送常规的写读事务到外部 DRAM,并比较从 DRAM 读取的数据和写入的数据是否一致。

BIST 模块的工作原理

- 回路回送模式(Loopback Mode):

在回路回送模式下,BIST 将数据从 PHY 的发送路径通过 I/O 返回到接收路径。这样,数据就可以在 PHY 内部进行循环回送,进行自检。这种模式不需要外部内存,因此适用于不需要依赖外部存储器的测试场景。 - DRAM 模式(DRAM Mode):

在 DRAM 模式下,BIST 会向 DRAM 发送正常的写读事务,并将读取的数据与预期数据进行比较。该模式适用于测试外部 DRAM 存储器。

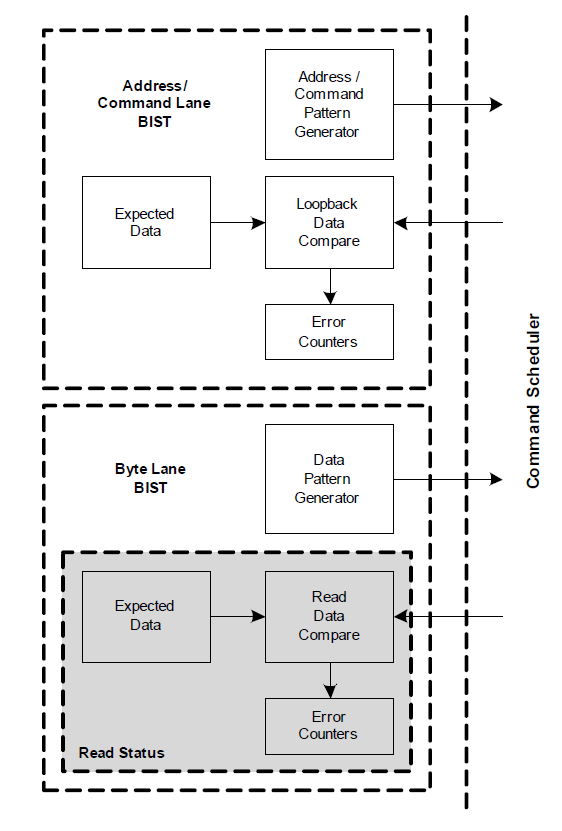

BIST 模块的结构(Block Diagram)

BIST 模块的框图(提供详细图示)展示了各个功能模块之间的连接方式。它通常包括以下几个主要组件:

- 传输路径(Transmit Path):用于将数据从 PHY 的发送端发送出去。

- 接收路径(Receive Path):用于接收回送的数据并进行比较。

- 外部内存接口:如果使用 DRAM 测试模式,则通过外部内存接口与 DRAM 进行通信。

- 测试模式选择器:允许选择回路回送模式或 DRAM 模式。

- 控制寄存器:通过这些寄存器,可以控制 BIST 模块的启停,配置回送模式、DRAM 模式、错误检测等。

通过该图示,用户可以理解如何在不同测试模式下配置 BIST 模块,并进行 PHY 和 I/O 的功能验证。

BIST(内建自测试)的操作模式

BIST(Built-In Self-Test)是一种用于测试和验证集成电路功能的技术。根据所述信息,BIST有两种操作模式:环回模式(Loopback Mode)和DRAM模式(DRAM Mode)。以下是对这两种模式的详细解释。

1. 环回模式(Loopback Mode)

环回模式是用来测试 PHY(物理层)和 I/O 接口的。其原理是将写入的数据直接送回接收路径,这样就不需要外部存储器(例如 DRAM)来进行测试。具体来说:

- DATXn 写路径和接收路径的环回: 在环回模式下,DATXn(数据线组)的写入数据将直接通过 I/O 传输到接收路径上。也就是说,BIST 发送数据之后,数据直接回到发送端,而不经过外部存储器,这样可以用来验证 PHY 数据通道是否正常。

- AC 输出路径的环回: 另外,AC 输出路径也会在 I/O 处被环回到专用的 AC 环回逻辑。AC 是指命令和地址通道(Address/Command),它用于传输内存的读写地址和控制信号。这部分的环回确保地址和命令通道也能正确工作。

这种模式的好处是无需连接外部 DRAM,测试过程可以在没有外部存储器的情况下进行,适合用于检查 PHY 层和 I/O 接口的基本功能。

- 最小的 WL/RL: 环回模式下支持的最小 WL(写延迟)和 RL(读延迟)为 6。WL/RL 是内存操作的延时设置,通常与内存的时序参数有关。BIST 测试时,环回模式对延迟有最低要求。

2. DRAM模式(DRAM Mode)

在 DRAM 模式下,BIST 会像正常的内存访问一样进行读写操作,写入数据到 DRAM 中,并从 DRAM 中读取数据来进行对比。这个模式实际上测试的是内存的数据完整性以及内存与 PHY 接口之间的配合。具体来说:

- 写读事务: 在 DRAM 模式下,BIST 会执行正常的写读事务(Write/Read Transactions)。即,它将数据写入 DRAM 并从 DRAM 中读取数据来进行对比,确保内存和 PHY 层能够正常交互。

- 地址和命令通道的环回: 即使是在 DRAM 模式下,地址/命令通道(Address/Command Channel)依然会在 I/O 处进行环回。这意味着,BIST 不会向外部发送命令和地址信号,而是会将这些信号发送回自身,以确保地址/命令通道的功能正确。

- 外部存储器测试: 在 DRAM 模式下,可以将其用作测试外部内存(例如,外部的 DRAM 存储芯片),通过发送写读事务并进行数据比较,验证 DRAM 和 PHY 层的通信是否正确。

BIST 运行的触发与配置

1. 触发 BIST 运行:

- 通过写入 BIST 运行寄存器(

BISTRR)并选择 RUN 操作来触发 BIST 运行。

2. 运行配置选项

- 无限运行

- BIST 可以配置为无限期运行,直到接收到 STOP 命令为止。

- 停止条件

- 可以配置为在检测到失败时停止。

- 也可以设置为在发出一定数量的测试模式后自动停止。

- 或在达到预设的最大地址值时自动停止。

3. BIST 模式选择

- 可选择的测试模式包括:

- 行走1(Walking 1s)

- 行走0(Walking 0s)

- 伪随机(Pseudo-random)

- 用户定义(User defined)

数据字节BIST运行过程

1. 写入操作

- 数据字节BIST从

BISTARn寄存器中设置的地址开始,执行一系列写入(WR)操作,直到发送的字数达到BISTWCR.BWCNT。

2. 地址递增

- 地址根据

BISTAR1.BAINC递增,同时自动处理bank的关闭或打开以及行激活。

3. 回环模式

- 在回环模式下,一旦发送的字数等于

BWCNT, BIST操作结束,回环数据与写入数据进行比较,记录任何失败。

4. DRAM 模式

- BIST现在会执行一系列读取(RD)操作,从DRAM中读取之前写入的数据,并与写入的数据进行比较,记录任何失败。

无限模式

- 在无限模式下(

BISTRR.BINF== 0x1),写入-读取序列将无限进行,直到满足某一停止条件:- 用户发出 BIST STOP(

BISTRR.BINST == STOP)。 - 比较失败的次数达到预设限制(

BISTRR.NFAIL),如果BISTRR.SONF == 0x1。 - 在 RD 操作中,地址达到预设的最大值(

BISTRR.BSOMA == 0x1),允许 BIST 通过完整的内存数组。

- 用户发出 BIST STOP(

错误状态与计数

1. 错误计数器:

位错误计数器

- 每个 DRAM 引脚有一个位错误计数器,例如,DATX8 上有9个计数器(8个数据位和1个数据掩码位),地址/命令通道最多可有34个计数器。

- 位错误计数器设计较小,以限制设计尺寸,每个计数器为2位宽,因此可以记录每个引脚上的最多3个错误。

字错误计数器

- 计数整个字的错误,如果数据字节通道或地址/命令通道的任何位发生错误,则相应的字错误计数器会增加。

- 字错误计数器为16位宽,可以计数最多64K个错误。

2. 数据掩码:

- 提供数据掩码功能,以便在某个位上记录更多错误,通常在诊断阶段使用。

BIST状态与重置

1. 完成状态:

- 一旦 BIST 模式执行完毕(停止或执行最后的测试模式),完成状态位(

BDONE)将被设置在 BIST 状态通用寄存器(BISTGSR)中,这是测试模式执行结束的唯一有效指示。

2. 轮询状态:

- 用户必须轮询此位,确保它被设置后才能读取其他状态寄存器。

3. BIST 重置指令:

- 提供 BIST 重置指令,通过

BISTRR寄存器,重置某些 BIST 状态寄存器位为默认值。

4. 系统重置:

- 注意,所有状态寄存器在系统重置时也会被重置为默认值。

总结

BIST的环回模式和DRAM模式提供了两种不同的测试方法:

- 环回模式:用于在没有外部内存的情况下测试PHY的内部逻辑,通过环回来验证数据传输的完整性。

- DRAM模式:用于实际测试外部DRAM的读写操作,通过发送和接收数据来验证内存的功能。

本文链接: https://talent-tudou.github.io/2024/10/27/DDR/PUB Architecture-DDR BIST/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!