DDR Training概述

DDR使用的是并行接口进行数据传输,这意味着多个数据位(64bits或者是128bits)同时在一组信号线上进行传输。随着总线频率的增加,信号在PCB(印刷电路板)上的传输变得更加复杂,因为PCB走线的长度差异,PVT(工艺,电压,温度)变化等因素会导致信号传播时间(即延迟)的差异。

当信号时序没有被正确对齐,或者是信号质量因为上述的原因而下降的时候,DDR控制器在采样点读取的数据可能会出错,导致读写操作异常,这是因为DDR在每个时钟周期的上升沿和下降沿都会进行数据传输,任何微小的时序偏差都可能导致数据被错误地采集。

为了解决上述问题,DDR系统就引入了Traning机制。Traning的主要目的是在DDR初始化过程中,动态调整DRAM与PHY之间的数据与地址命令信号线的时序关系,以确保信号在正确的时间被采样。

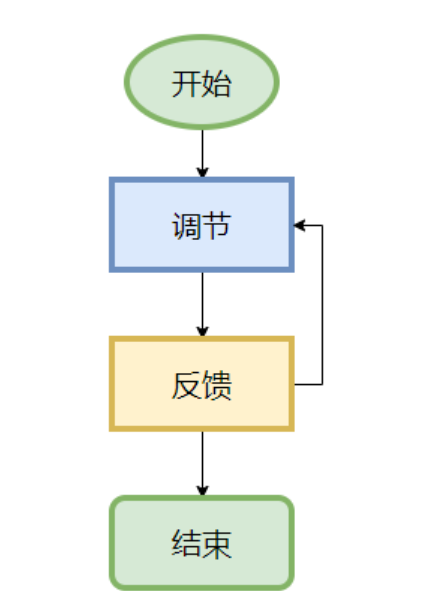

training的大致流程:

记住下面几个问题

Training的对象

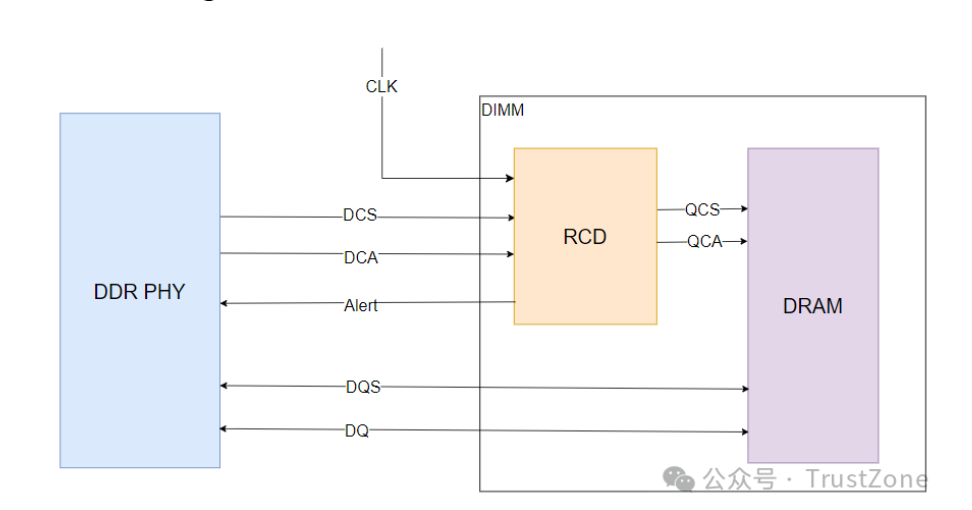

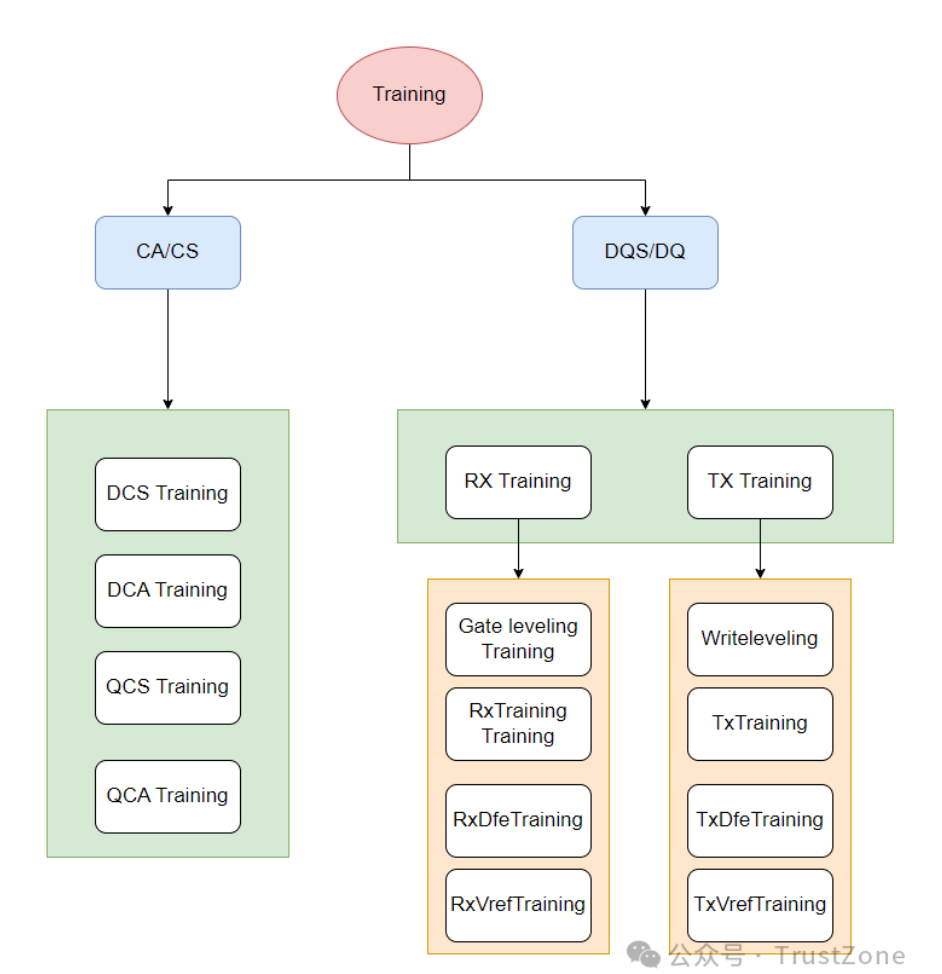

对象是DDR PHY和DRAM之间的交互信号线

- CK:时钟信号

- CS:片选信号,RANK选择

- AC:Address和Command

- DQS:对数据的采样信号

- DQ:数据线

- Alert:用于training过程中,反馈DCS和DCA到达RCD的回应。正式业务场景是不需要的(这个就像是上面流程图的反馈,当然反馈的功能不只是training,有时候这个信号也会作为ecc的反馈)。

本文作者:

ICXNM-ZLin

本文链接: https://talent-tudou.github.io/2024/10/22/DDR/DDR-Traning/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!

本文链接: https://talent-tudou.github.io/2024/10/22/DDR/DDR-Traning/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!