DDR介绍

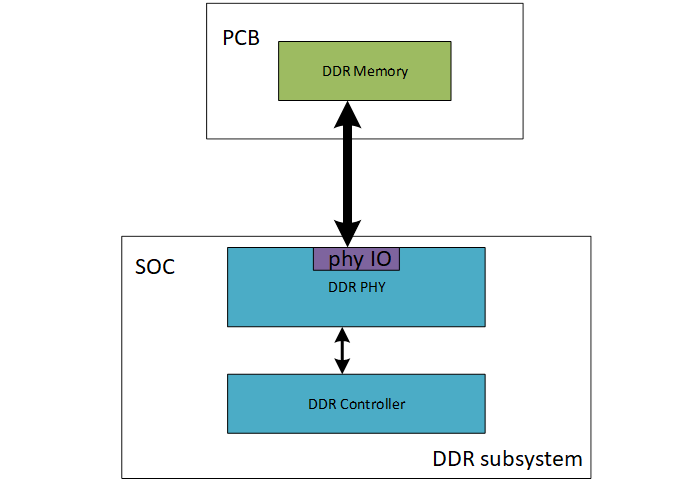

DDR子系统是由两个部分组成的,ddr controller和ddr phy。ddr controller主要是负责承担CPU(或者说是外部)和memory系统之间进行数据交互时候的传输效率和调度的。ddr phy主要是负责数据交换过程中的传输速度了。(如下图)

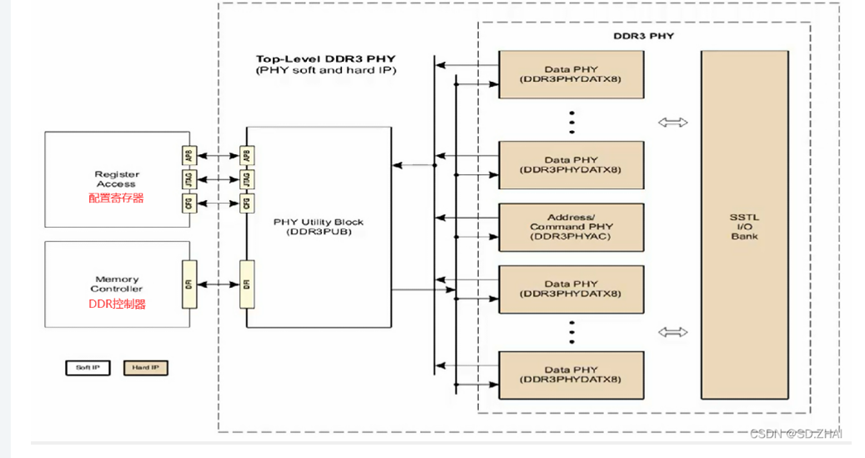

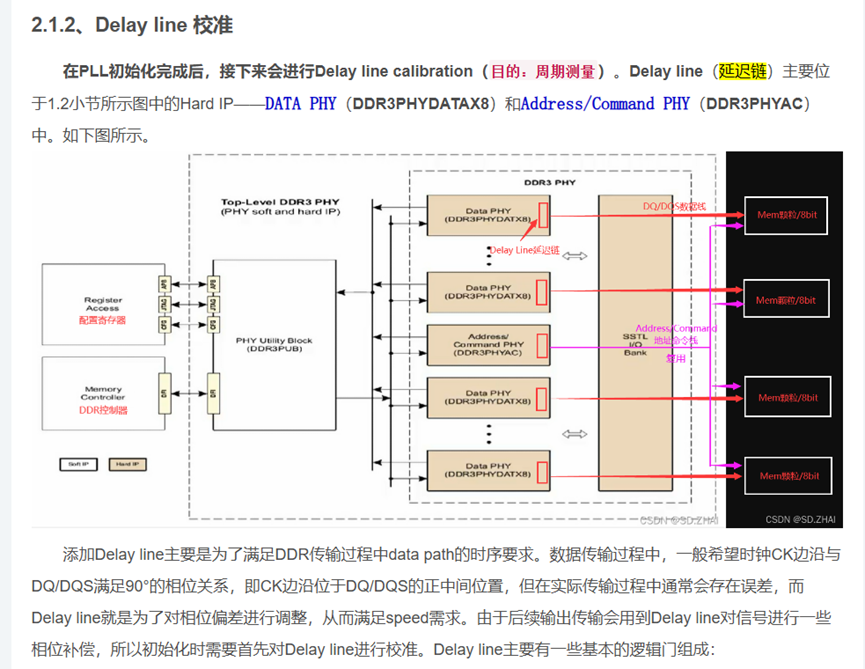

ddr phy主要是由两个部分来组成的,一个pub(soft ip)和另外一个phy(hard ip)。

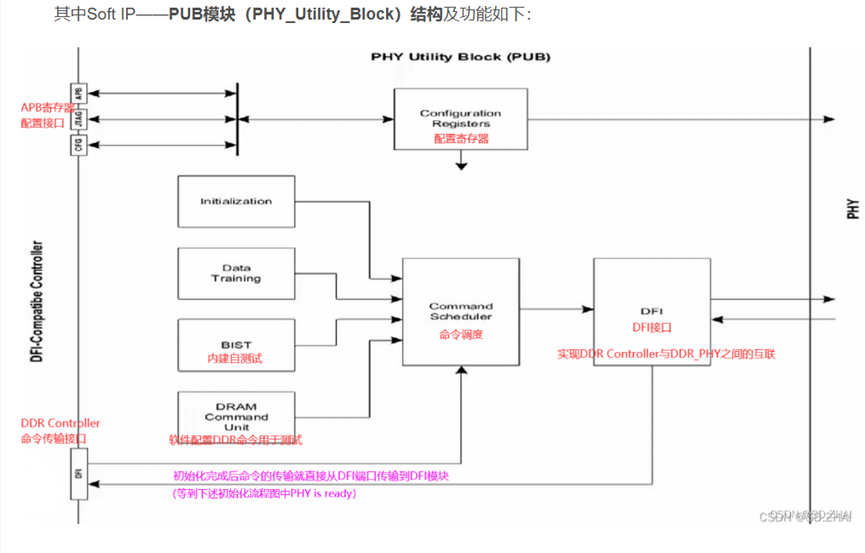

其中pub的结构如下图所示:

pub具有一下特点:

- 不支持SDRAM的DLL off模式

- 数据通路的位宽以8bit的增量递增

- 支持最多4个rank

- 支持单数据通道或者双数据通道的配置

- 能够完成PHY的初始化,tranning以及控制逻辑

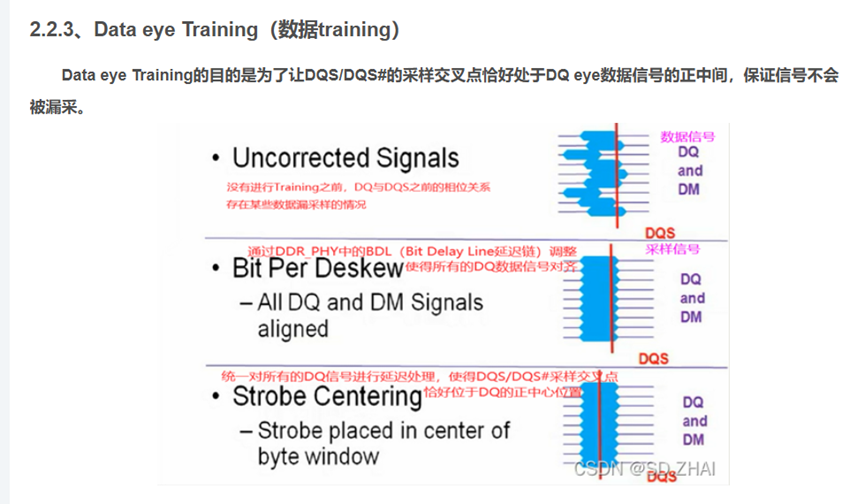

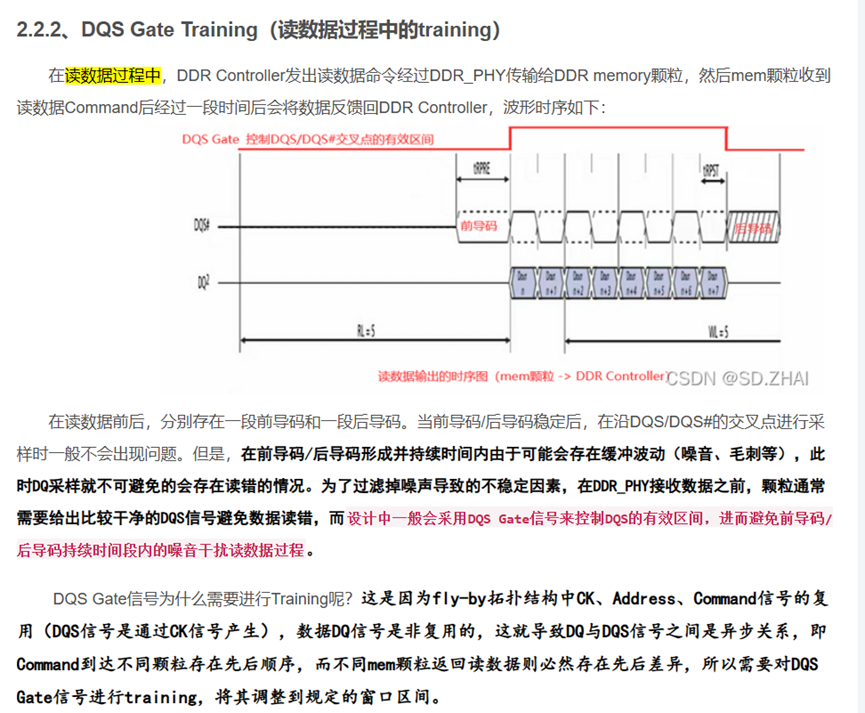

- 支持自动化的DQS Gate Tranning

- 支持Delay line和VT补偿

- 支持自动化的Write Leveing

- 支持自动化的Write,Read的data bit deskew

- 支持自动化的DQ/DQS eye tranning

- 支持apb或者其他的通用接口配置寄存器

- 支持DFI接口

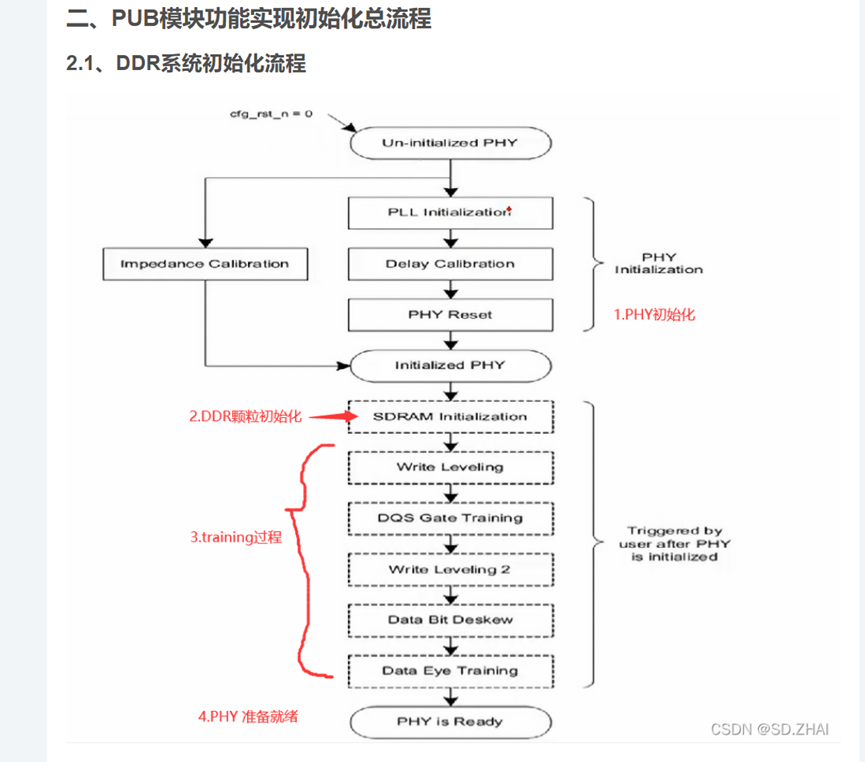

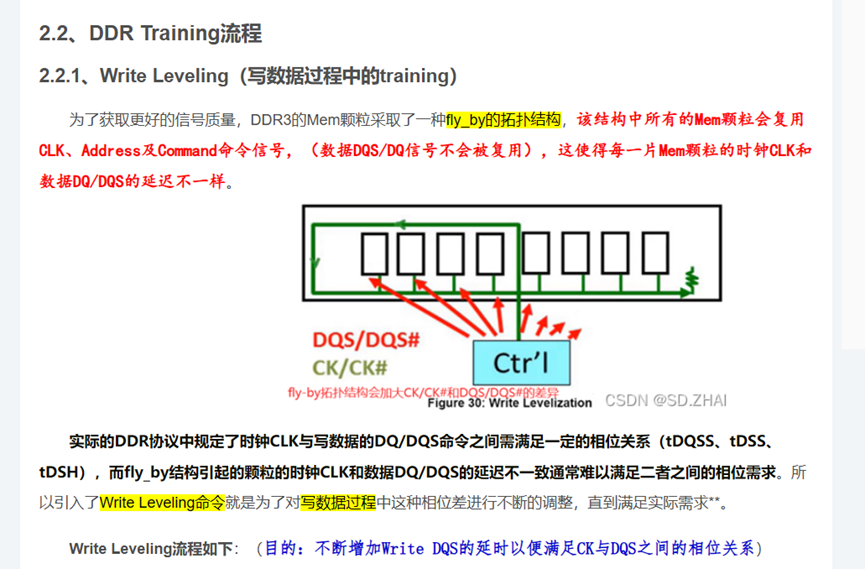

PUB模块实现初始化流程

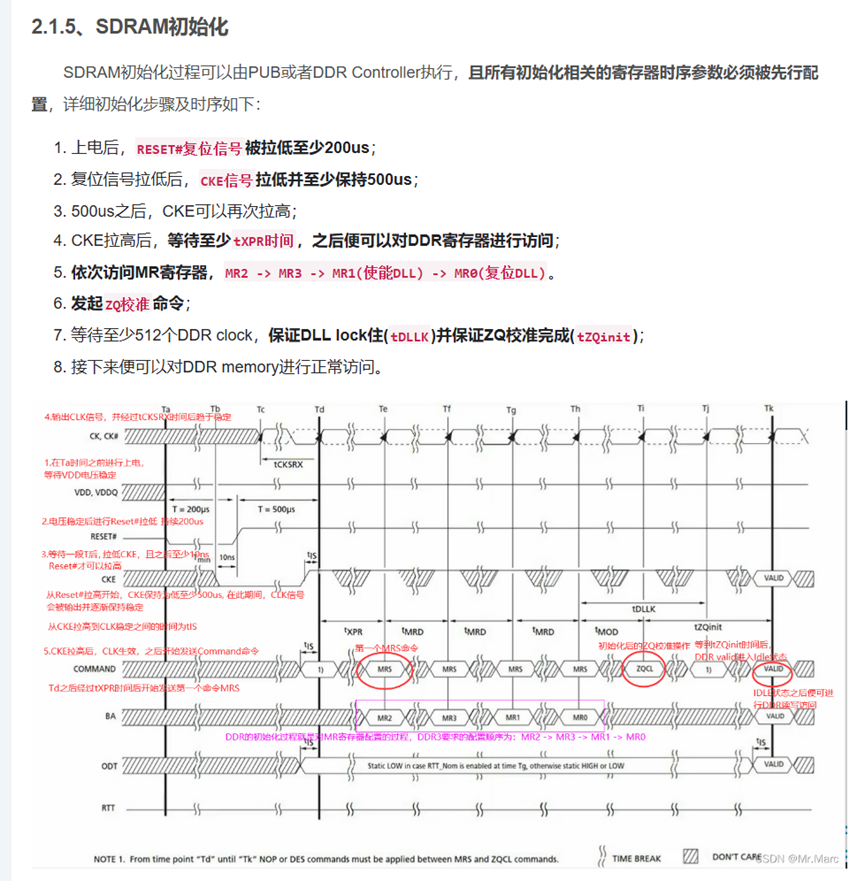

DDR系统初始化

本文作者:

ICXNM-ZLin

本文链接: https://talent-tudou.github.io/2024/10/19/DDR/DDR科普-DDR PHY/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!

本文链接: https://talent-tudou.github.io/2024/10/19/DDR/DDR科普-DDR PHY/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!